# Dora: A Simple Approach to Zero-Knowledge for RAM Programs

Aarushi Goel\* Mathias Hall-Andersen<sup>†</sup> Gabriel Kaptchuk<sup>‡</sup>

#### **Abstract**

Existing protocols for proving the correct execution of a RAM program in zero-knowledge are plagued by a *processor expressiveness tradeoff*: supporting fewer instructions results in smaller processor circuits (which improves performance), but may result in more program execution steps because non-supported instruction must be emulated over multiple processor steps (diminishing performance).

We present Dora, a very simple and concretely efficient zero-knowledge protocol for RAM programs that sidesteps this tension by making it (nearly) free to add additional instructions to the processor. The computational and communication complexity of proving each step of a computation in Dora, is *constant* in the number of supported instructions. Dora's approach is united by intuitive abstraction we call a ZKBag, a cryptographic primitive constructed from linearly homomorphic commitments that captures the properties of a physical bag. We implement Dora and demonstrate that on commodity hardware it can prove the correct execution of a processor with thousands of instruction, each of which has thousands of gates, in just a few milliseconds per step. Our evaluation shows that Dora has notably better end-to-end performance than concurrent work targeting the same problem.

$<sup>*</sup>Purdue\ University\ aarushi@purdue.edu$

<sup>†</sup>Galois, zkSecurity and Aarhus University mathias@hall-andersen.dk

<sup>&</sup>lt;sup>‡</sup>University of Maryland, College Park kaptchuk@umd.edu.

# Contents

| 1 | Introduction                                    | 3  |

|---|-------------------------------------------------|----|

|   | 1.1 Our Contributions                           | 4  |

|   | 1.2 Related Work                                | į  |

| 2 | Technical Overview                              | e  |

|   | 2.1 Background: Template for RAM Zero-knowledge | 6  |

|   | 2.2 Zero-Knowledge Bag                          |    |

|   | 2.3 Constructing Dora using ZKBag               | 8  |

| 3 | Preliminaries                                   | 10 |

|   | 3.1 Linearly Homomorphic Commitments            | 11 |

|   | 3.2 Relaxed R1CS                                |    |

|   | 3.3 Commit-and-Prove Zero-Knowledge             | 12 |

|   | 3.4 Commit-and-Prove ZK for R1CS                | 13 |

|   | 3.5 Multi-Set Equality Proofs                   |    |

| 4 | Zero-Knowledge Bag                              | 14 |

|   | 4.1 Defining ZKBag                              | 14 |

|   | 4.2 Realizing a ZKBag Protocol                  | 16 |

| 5 | Verifying Memory Consistency using ZKBag        | 19 |

| 6 | Verifying Processor Execution using ZKBag       | 20 |

| 7 | Dora: Zero-Knowledge for RAM Programs           | 25 |

| 8 | Implementation and Evaluation                   | 27 |

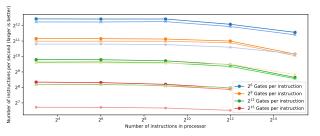

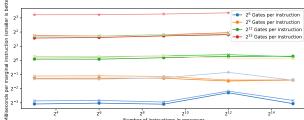

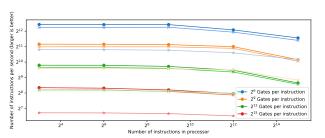

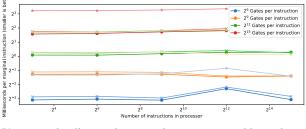

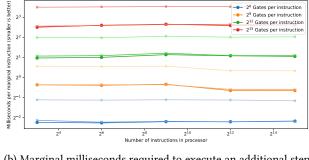

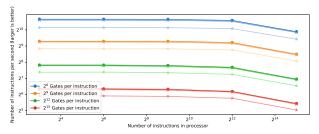

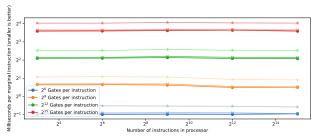

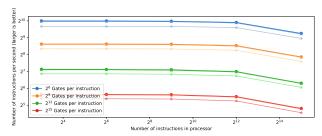

|   | 8.1 Verifying Processor Execution               | 29 |

|   | 8.2 Verifying Memory Consistency                |    |

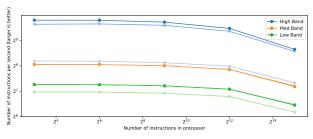

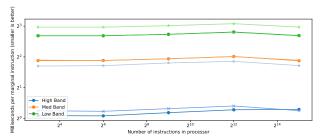

|   | 8.3 Comparison with Other Approaches            |    |

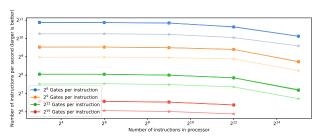

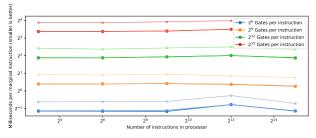

| A | Additional Benchmarks and Evaluation            | 40 |

|   | A.1 Additional Bandwidth Benchmarks             | 40 |

|   | A.2 Comparison with Concurrent Work             |    |

|   |                                                 |    |

### 1 Introduction

Zero-knowledge proofs and arguments<sup>1</sup> [GMR85, GMW86] empower a prover to demonstrate to a verifier that executing a public program p on some secret inputs x yields a particular output y, i.e., p(x) = y. A long line of work has demonstrated feasibility of practically efficient zero-knowledge systems [GS08, JKO13, GGPR13, BCC<sup>+</sup>16, Gro16, KKW18, BBB<sup>+</sup>18, BCR<sup>+</sup>19, GWC19, Set20, HK20c, BMRS21, WYKW21, YSWW21, WYX<sup>+</sup>21, WYY<sup>+</sup>22, BBMHS22, YHKD22]. As a result, zero-knowledge proofs are now being integrated as a key component of deployed systems [BCG<sup>+</sup>14, Zav20, se19].

Most existing zero-knowledge proof systems require that *p* is represented as an arithmetic or boolean circuit (or an equivalent algebraic constraint system). Most natural programs, however, are *RAM programs*, i.e., programs designed for von Neumann architectures. RAM programs capture the intuitive notion of computation used by most practitioners, in which a central processing unit (CPU) with a fixed set of instructions incrementally operates on a large, *random access memory* using load and store operations.

Closing the gap between the RAM programs about which provers and verifiers are interested and the circuit representations required by zero-knowledge provers is a key hurdle to making zero-knowledge more deployable. This gap is more than semantic, as some algorithms in the RAM model are more efficient than comparable circuit representations (e.g., sorting). In other circumstances, the prover and verifier might be particularly interested in an existing RAM program, e.g., proving knowledge of a software exploit against a deployed RAM program [HK20c, GHAH+23, HYDK21, HK21] or proving that software is legally compliant [BCG+22, BCGW22].

**Zero-knowledge for RAM Programs.** In order to facilitate proving executions of RAM programs in zero-knowledge, we use techniques that reduce RAM programs to the circuit representations used within zero-knowledge systems. One straightforward approach is to leverage *circuit compilers* [MGC<sup>+</sup>16, Wan]: transform the source code describing a RAM program into a circuit capturing the same functionality. Correct evaluation of the resulting circuit can then be proven using any existing zero-knowledge system for circuits, as done in [HK20c]. This approach, however, introduces several, noteworthy inefficiencies: the resulting circuit must be input-independent, all loops must be unrolled for a fixed number of iterations, and all input-dependent conditional branches are part of the circuit description.<sup>2</sup> These constraints can significantly increase the size of the resulting circuit, and therefore increase the complexity of proving their evaluation in zero-knowledge.

Instead, the state-of-the-art approach to proving the execution of RAM programs in zero-knowledge [BCG<sup>+</sup>13, BCTV14b, BCTV14a, HK20a, HYDK21, HK21, FKL<sup>+</sup>21, DOTV22] emulates the execution of the RAM program on a custom processor. First, the prover and verifier agree upon a circuit representation of the CPU and RAM access module. Then, the prover demonstrates that a step of the computation was executed correctly by showing that the program state (comprising the state of memory and any additional registers in the CPU) is the outcome of a *valid state transition* from the previous program state, where the valid transition functions are determined by the processor's instruction set. This process is repeated until program execution has completed.

The Expressiveness Tradeoff. Designing an optimized processor to use when proving execution of RAM programs in zero-knowledge requires grappling with an *expressiveness tradeoff*. It is natural to want a very *small* processor circuit with very few instructions, as the prover must "pay" for all the instructions in the processor in each step of the proof—even unused instructions. This is because proving each state transition using modern zero-knowledge proof systems—including SNARKs—will have prover complexity proportional to total size of the processor. As such, minimizing processor size has become standard practice; Ben-Sasson et al. [BCG+13, BCTV14b] introduced a processor called TinyRAM with only 29 instructions for this purpose, and recent works have created other processors with even fewer instructions [HK20a, HYDK21, FKL+21]. This approach, however, results in *more* steps of program execution—potentially negating the value of a smaller circuit representation of the processor—because instructions not included in the processor must be *emulated* over multiple processor steps. Finding the right balance between processor expressiveness (i.e., how many instructions it supports) and program length is a highly nuanced engineering problem and will depend on the specific RAM program.

In this work, we propose a simple, new approach to RAM zero-knowledge that avoids the expressiveness tradeoff altogether. Our work leverages the observation that the processor circuit has a very specific structure; namely,

<sup>&</sup>lt;sup>1</sup>We use the terms proofs and arguments interchangeably in this work, as is common in practically oriented work on zero-knowledge.

<sup>&</sup>lt;sup>2</sup>As discussed below, some recent work has shown how to avoid the communication costs associated with branching.

that it is a *disjunction* of the supported instructions. A sequence of recent works on disjunctive zero-knowledge [HK20c, BMRS21, GGHAK22b, KST22, KS22, GHAKS23, KS23] have shown that it is possible to design zero-knowledge protocols with prover complexity proportional only to the size of the largest clause in the disjunction. Within the context of RAM zero-knowledge, this would allow adding additional instructions to the processor circuit for free, thereby increasing expressiveness.

#### 1.1 Our Contributions

We present Dora, a conceptually simple and concretely efficient zero-knowledge proof system for RAM programs with a *non-succinct* proof size. We focus on designing a non-succinct proof system because they have been shown by several recent and groundbreaking works [DIO21, YSWW21, YHH+23, BMRS21, WYKW21, DOTV22] to yield significantly better proof generation times as compared to succinct zero-knowledge (i.e., zkSNARKs).<sup>3</sup> Dora provides a new way out of the *expressiveness tradeoff* by supporting increased processor expressiveness for free (both in terms of computation and communication). Dora has the following desirable attributes:

- Communication and Computation Complexity of  $O(t+\ell)$ , where t is the number of steps of the computation and  $\ell$  is the number of instructions supported by the processor. The verifier sends just a single field element in each step of the computation and the prover's per-step communication and computation depends only on the size of the instruction being executed in that step. Note that naïve approaches would have prover and communication complexity  $O(t\ell)$ , making Dora a significant improvement.

- Generic Approach and Fiat-Shamir Friendly: Our approach combines new techniques with insights from recent work on disjunctive zero-knowledge [HK20c, GGHAK22b, GHAKS23] and incrementally verifiable computation [KST22, KS22]. Dora only assumes the existence of a linearly homomorphic commitment scheme, the optimal choice for which can be selected based on the deployment considerations. For example, if Dora was deployed in an interactive setting, VOLE-based techniques [BCGI18, YWL+20, BMRS21, YSWW21, WYKW21, BBMH+21] can be used, whereas Pedersen commitments [Ped92] can be substituted when non-interactivity is desirable. If the commitment scheme is post-quantum secure, then Dora will also be post-quantum secure. Finally, the verifier in Dora is public coin, making it Fiat-Shamir friendly [FS87].<sup>5</sup>

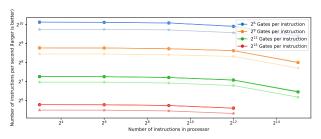

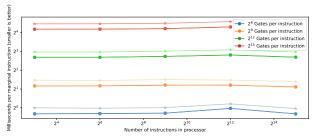

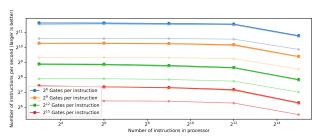

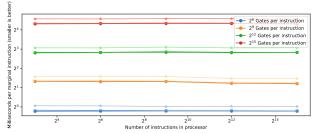

- Concretely Efficient: Dora is concretely efficient. We implement Dora and integrate it into the swanky [Gal19] framework. The marginal cost of proving an additional step of computation with Dora is on the order of milliseconds. For example, if each instruction has 2<sup>9</sup> gates, then Dora, when run on commodity hardware (slower than a typical laptop), can prove correct execution of a program at >2000 steps per second—no matter how expressive the processor instruction set.

**Simple Approach.** Our approach for efficiently realizing a zero-knowledge protocol for RAM programs is exceedingly simple. We identify a single abstraction through which we can unify our approach to proving that memory has been handled honestly and the processor circuit has been correctly applied. We call this abstraction a *zero-knowledge bag* (ZKBag). The natural *physical analogy* of the ZKBag is an opaque bag filled with identical envelopes. A prover can insert envelopes (i.e. commitments) into this bag and later remove envelopes. Because the bag's material is opaque and all envelopes are identical, an observer cannot determine when a removed envelope was initially inserted but knows that anything removed must have, at one point, been inserted. We construct Dora from two ZKBags as follows:

- (1) To ensure that memory is treated consistently, the prover and the verifier keep the active state of memory within the first ZKBag. To manipulate a memory cell, the prover simply finds the envelope holding that cell within the bag and removes it, updates it appropriately, and returns it to the bag.

- (2) We let the second bag hold the intermediary states for a set of  $\ell$  batch proof protocols, each corresponding to an instruction supported by the processor. In each processor step, the prover removes the state for the appropriate instruction, adds another instance of the instruction into the state, and returns the updated state to the bag. Once all steps are complete, each of the  $\ell$  batch proofs are verified.

$<sup>^3</sup>$ We leave the problem of designing a succinct zero-knowledge for RAM programs with similar concrete prover efficiency to future work.

<sup>&</sup>lt;sup>4</sup>We assume that all instructions are of the same size. This assumption holds without loss of generality, as we can always pad smaller instructions to match the size of the largest instruction.

$<sup>^5 \</sup>mbox{We provide}$  a more detailed discussion on the application of the Fiat-Shamir transform to Dora in 8.

Concurrent Work. Two recent works [YHH<sup>+</sup>23, YH23], developed concurrently with our own, focus on designing more efficient zero-knowledge random access memory [YH23] and for proving statements with processor-like structures [YHH<sup>+</sup>23]. Although not done, it is straightforward to combine these two works to achieve a RAM zero-knowledge protocol.<sup>6</sup>

A crucial difference between these works and Dora, lies in the relative simplicity of our approach. For instance, in [YHH+23], Heath et al. demonstrate how to adapt specific techniques from VOLE-based zero-knowledge proof systems [DIO21, YSWW21] for proving statements with processor-like structures with optimal asymptotic complexity. Similarly, they develop separate techniques for independently handling memory accesses. In contrast, our goal in this work was to identify the simplest fundamental approach for designing zero-knowledge for RAM programs with the desired asymptotic complexity. For this, as discussed above, we formalize a single unifying primitive called zkBag and demonstrate that it suffices for proving consistency of both processor execution and memory accesses.

We think that this clean and simple abstraction effectively highlights the main challenges that must be overcome for efficiently implementing zero-knowledge for RAM programs. This, in turn, may contribute to further enhancing the practical efficiency of zero-knowledge for RAM programs in future works—perhaps by combining our approaches. We include a concrete, best-effort comparison to these concurrently developed works in Appendix A.2. We find that Dora offers notably faster proving times  $(1.5x-10x)^7$  for processor execution but is slower ( $\approx 2x$ ) at updating memory. In both approaches, proving the processor execution is the main performance bottleneck (proving correct execution of processor step takes milliseconds while memory update takes microseconds), meaning Dora may offer a more promising path to production quality systems.

#### 1.2 Related Work

Zero-knowledge for RAM programs emerged as a problem of interest following the work of Ben-Sasson et al. [BCGT13, BCG+13, BCTV14b, BCTV14a], which demonstrated that it was feasible to prove the correct execution of real RAM programs. These works laid out the primary template from which we work (discussed in Section 2.1 below). Recent works have improved performance, including the work of Heath et al. [HK20a, HYDK21, HK21], Franzese et al. [FKL+21] and Delpech de Saint Guilhem et al. [DOTV22]. These works have demonstrated concrete efficiency, but still must pay the cost of the full processor circuit in each step. Another common approach to proving correct execution of RAM programs is to "unroll" the program into an explicit circuit which can be prover with generic zero-knowledge techniques, e.g., [CK18, YSWW21, WYKW21]. The demonstration that these approaches are efficient has led to studying new applications of zero-knowledge, e.g., proofs that a program can be exploited [HK20c, GHAH+23, CHP+23].

To reduce the complexity of executing one step of the processor to be independent of the number of instructions, we leverage the disjunctive structure of processors. Zero-knowledge that is optimized for disjunctions has been the focus of foundational work on zero-knowledge [CDS94, AOS02, GMY03] and a significant number of recent work [GK15, CPS+16, Kol18, HK20c, GGHAK22b, ACF21, BMRS21, GHAKS23]. Generally, these works exploit the observation that the *prover* knows which clause of the disjunction is satisfied, and therefore the work on the remaining clauses is "wasted." This means that protocols can be designed, e.g., [HK20c, GGHAK22b, ACF21, BMRS21], that have communication complexity the depends mostly on the size of the largest clause in the disjunctions (possibly with logarithmic overhead). Our work can be seen as developing specialized disjunctive zero-knowledge techniques that compose well with RAM access and have efficient computation time.

**Incrementally Verifiable Computation.** Our works builds on two recent results on building incrementally verifiable computation (IVC) from folding schemes, Nova [KST22], SuperNova [KS22], Protostar [BC23] which are a part of an emerging literature on concretely efficient IVC [BGH19, BCMS20, BDFG21, BCL<sup>+</sup>21]. In Nova [KST22], Kothapalli et al. show how to build a folding scheme for NP using a generalization of R1CS called *Relaxed R1CS* and show how it can be used to build IVC. SuperNova [KS22] and Protostar [BC23] were then proposed as extensions of Nova that support *non-uniform* IVC for "free," and discuss how to apply their techniques to verifying processor

<sup>&</sup>lt;sup>6</sup>In a follow-up work [YHH<sup>+</sup>24], the authors of [YHH<sup>+</sup>23, YH23] explore this approach.

<sup>&</sup>lt;sup>7</sup>The conference version of this work had a typo in Figure 11 table which was propagated throughout the rest of the text. This has been fixed in this version.

<sup>&</sup>lt;sup>8</sup>The initial version of this paper shared publicly reported that Dora offered slower proving times for both processor execution and updating memory that concurrent work. This was due to an error in our evaluation that compared the performance of Dora on an 128-bit field to concurrent work on a 61-bit field. The evaluation presented in this version is more accurate.

computations.

Zero-knowledge proofs for RAM program execution can be seen as a version of non-uniform IVC where the prover must also hide *which* instructions are applied to the state at each step of the computation, but also need not be fully succinct in the number of steps. Zero-knowledge is not a goal of SuperNova, and thus we require new techniques to leverage their approach into our setting. Additionally, SuperNova's IVC reasons over the entire contents of memory, which is not concretely efficient; instead, we couple our zero-knowledge IVC with a separate protocol for managing memory consistency. Kothapalli and Setty have also recently introduced HyperNova [KS23], which aims to develop new folding schemes for NP that can be used to build more efficient IVC.

Other SNARKs. There are other prior works [WSR<sup>+</sup>15, ZGK<sup>+</sup>18, KPPS20, BBHR18, lib18, gen20, hod21, GPR21, MAGABMMT23, DXNT23, CGG<sup>+</sup>24] that focus on building concretely efficient zkSNARKs (zero-knowledge succinct non-interactive arguments of knowledge), where the prover cost grows only with the size of the program execution. For instance, Buffet [WSR<sup>+</sup>15], vRAM [ZGK<sup>+</sup>18], Mirage [KPPS20], MUX-Marlin [DXNT23] and Sublonk [CGG<sup>+</sup>24] that consider an "a la carte" cost profile for the provers where the prover cost for proving a step of computation grow only with the size of the circuit representing the instruction invoked on that step, i.e. independent of the number of branches. However, these schemes require a trusted common reference string setup and make use of expensive public-key operations. Works building on zkSTARKs [BBHR18, lib18, gen20, hod21, GPR21, MAGABMMT23] use a transparent (i.e. untrusted) setup and require the prover to only do work proportional to the execution trace. However, they require making a non-black box use of cryptographic hash functions. Similarly, commit and prove style SNARKs that [CFQ19, Lip16, CFH<sup>+</sup>15] that have similar prover computation times also make non-black box use of cryptographic commitments. Therefore, while all of these schemes have sublinear proof sizes, their prover computation times are significantly worse than those resulting from known techniques for zero-knowledge with non-sublinear sized proofs.

#### 2 Technical Overview

We now give an overview of the key techniques we use to construct Dora. We first recall the basic template to achieving zero-knowledge for RAM programs before proceeding to Dora itself.

## 2.1 Background: Template for RAM Zero-knowledge

As discussed earlier, while zero-knowledge has primarily been studied in the circuit model (i.e., where the relation for the NP language is represented as a circuit over a finite field), a significant line of work has studied how to achieve zero-knowledge for RAM programs [BCGT13, BCG $^+$ 13, BCTV14b, HK20a, HYDK21, GHAH $^+$ 23]. The key idea in these works is to bootstrap from circuit zero-knowledge to RAM zero-knowledge by representing the RAM machine on which the program should be evaluated as an explicit circuit. The prover can then use this circuit as a state transition function, and show (in zero-knowledge) that repeatedly applying this circuit t times to some initial inputs, results in a desired final processor state.

More concretely, the prover and verifier represent the RAM machine using two components: (1) a *processor circuit*  $C_{proc}$ , and (2) a *memory checker circuit*  $C_{mem}$ .  $C_{proc}$  takes as input, values fetched from memory and implements a set of valid instructions  $I = \{I_1, \ldots, I_\ell\}$ , ensuring that only one of these is evaluated at every step over the inputs. For example, the  $I_i$  instruction might add values, test values for equality, or modify the processor state to affect control flow, etc... The result of this evaluation can then be stored back in memory. The memory checker circuit  $C_{mem}$  enforces that memory is treated consistently—that is, when a value is read from a particular memory address,  $C_{mem}$  checks to make sure that the value corresponds exactly to the last value written to that memory address.

Because most approaches for instantiating zero-knowledge for RAM program relies on this bootstrapping approach, the key determinant of efficiency is the *size* of the circuits required to implement the functionality  $C_{\rm proc}$  and  $C_{\rm mem}$ .

- Current Approaches to  $C_{proc}$ . Prior work has emphasized the need for a *small*  $C_{proc}$ , at the expense of expressiveness. For example, Ben-Sasson et al. [BCG<sup>+</sup>13] describe a minimal  $C_{proc}$  called TinyRAM, which contains 27

<sup>&</sup>lt;sup>9</sup>Hardware architectures also have local memory, i.e., registers and program counter, within the processor circuit. For the purposes of this overview, we elide these low level details, but note that they can either be handled as *state* within the processor circuit or simply as a specially named memory region.

instruction that can be represented in  $\leq 972$  gates. <sup>10</sup> This is because the final circuit contains t copies of  $C_{proc}$ , and t can be very large (e.g. imagine t is in the hundreds of thousands, or more). Thus, if a particular instruction  $I_i$  is very rarely used (in an average program), the prover and verifier still pay for that instruction in each step of the program execution. It may be more efficient to instead  $emulate\ I_i$  using a sequential series of other instructions, increasing the value of t while effectively reducing the costs of each of the t steps. In practice, this emulation approach is concretely efficient—executing a RAM program on a TinyRAM only increases t by a multiplicative factor of 2-6x compared to x86, which contains hundreds of instructions.

- Current Approaches to C<sub>mem</sub>. There are two primary approaches to checking the consistency of memory accesses discussed in prior works: (1) leverage an efficient oblivious RAM (ORAM) construction, or (2) use a permutation proof. In the former approach, the prover stores tuples of the form (ADDRESS, VALUE) within an ORAM (eg. [MRS17]), which is either maintained by the verifier (if the proof will be executed interactively) or represented in a non-black box manner within C<sub>mem</sub>. Since ORAM constructions hide access patterns and can guarantee consistency, the verifier can be confident that memory has been treated honestly without learning anything about the program execution. The other approach has the prover generate a memory trace of all reads and writes during program execution. The prover then permutes this trace to be sorted by address (tie-broken by timestamp), and C<sub>mem</sub> needs to only check that neighboring elements of the sorted trace are internally consistent. This latter approach has been found to be more efficient in practice, and is the primary approach used in work focused on concrete efficiency [FKL+21, DOTV22, GHAH+23].

#### 2.2 Zero-Knowledge Bag

At the heart of our construction is a new, unifying primitive that we introduce called a *zero-knowledge bag* (or ZKBag). We begin by describing this building block and then show how it can be used to instantiate Dora. We require that a ZKBag—the digital equivalent of a physical, opaque bag—provides the following (informal) guarantees:

- 1. *Unique Removal*: Once an element has been retrieved from the ZKBag, it cannot be retrieved again (unless, of course, it is re-inserted).

- 2. *Ordered Binding*: Every element that is retrieved from the bag is exactly one of the elements that was previously inserted into the ZKBag.

- 3. *Order Hiding*: The act of retrieving an element from the ZKBag reveals nothing about when that element was inserted.

Clearly, in order to realize the *order hiding* property, elements cannot be inserted into the ZKBag in the clear, or else a verifier could trivially link insertions and retrievals based on the value itself. As such, we insert and remove cryptographic *commitments*; when the prover wants to remove a value, it creates a *new*, *fresh* commitment to the value and convinces the verifier that the value therein corresponds to a value currently within the bag. This process should also remove the committed value from the bag.

Looking ahead, ZKBag provides the right combination between binding and pattern hiding required to construct zero-knowledge for RAM programs. The relationship between ZKBag and memory consistency should be clear: writing to memory corresponds exactly to inserting a (ADDRESS, VALUE) tuple into a ZKBag, and reading from memory corresponds exactly to retrieving a (ADDRESS, VALUE) tuple from a ZKBag. We will also use a ZKBag to hold the instruction set I for the processor, and have the prover pick out one instruction to be evaluated in each processor step (before reinserting it).

**Constructing a ZKBag.** It is clear to see that ZKBag is closely reminiscent of many existing cryptographic primitives. If *unique removal* were not required, ZKBag could be realized directly with *set membership proofs*, a concretely efficient primitive that has been the subject of immense recent study (eg. [RST01, CCs08, BCF<sup>+</sup>21, GGHAK22a, CGT23]). To achieve *unique removal*, it is clear that some kind of oblivious revocation is required, a technique that has been used in multiple other contexts, eg. ZCash [MGGR13]. However, a set membership based approach will require that the

<sup>&</sup>lt;sup>10</sup>For simplicity, we do not yet make a distinction between the number of gates needed to *compute* the instructions and the number of gates needed to *verify* that a claimed evaluation is correct. In practice, we always mean the latter.

statement for each retrieval *grows* as the protocol continues. It like the want each insertion and retrieval to require a *constant* amount of communication and computation, as these interfaces will be called many (ie. O(t)) times.

To achieve constant overhead, we batch checks required for ordered binding and unique removal across all insertions and retrievals, deferring the verification until the end of the protocol. In more detail, the prover and verifier maintain two lists of commitments: a list of insertions  $\mathcal{I}$  and a list of retrievals  $\mathcal{R}$ . Each time the prover wants to insert a value  $v_i$  into the ZKBag, the verifier provides a uniformly random tag tag<sub>i</sub> to the prover. The prover forms a hiding commitment  $com_{v_i}$  as  $com_{v_i} = Com(v_i)$  and the parties jointly form a public/non-hiding commitment  $com_{tag_i}$  as  $com_{tag_i} = Com(tag_i)$  with shared randomness. Both parties add  $(com_{tag_i}, com_{v_i})$  to their respective insertion list  $\mathcal{I}$ . When retrieving a value  $v_j$  from the ZKBag, the prover recalls the tag tag<sub>j</sub> generated during insertion, creates the hiding commitment tuple  $(com_{tag_j} = Com(tag_j), com_{v_j} = Com(v_j))$  using fresh randomness and both parties add  $(com_{tag_i}, com_{v_i})$  to the their respective retrieval list  $\mathcal{R}$ .

When the protocol ends, the prover retrieves any remaining values from the bag (i.e., it empties the bag) and gives a permutation proof demonstrating that there exists a permutation  $\phi$  such that  $\mathcal{I} = \phi(\mathcal{R})$ . It is easy to see that *read-only access* to the ZKBag can be accomplished by removing a tuple (com<sub>tag</sub>, com<sub>v</sub>) from the bag and immediately re-inserting the same (non-rerandomized) value commitment with a freshly generated tag (ie. the tuple (com<sub>tag</sub>, com<sub>v</sub>)).

Intuitively, the use of hiding commitments provides the necessary order hiding property, and the tags provides both the ordered binding and unique removal properties. Specifically, a prover who wanted to remove an item that has not yet been inserted would need to predict the tag that the verifier would generate for that value in the future. Similarly, if an adversary removes the same value from the ZKBag twice, it must produce a second valid tag corresponding to the value. If the prover re-uses the same tag twice, there will be a mismatch in the tags in  $\mathcal I$  and  $\mathcal R$ , and if it uses a new tag, it must predict a tag the verifier will generate in the future. This construction is highly efficient. Each insertion and removal requires preparing and sending only two commitments. The batched check can be done with constant communication and linear computation using a Neff-style commit-and-prove style permutation proof [Nef01] (which we describe in Section 3.5).

## 2.3 Constructing Dora using ZKBag

In our work, we approach the problem of constructing efficient zero-knowledge for RAM programs at the *protocol* level, rather than trying to optimize the choice of circuits  $C_{\rm proc}$  and  $C_{\rm mem}$ .

**Expressiveness Comes Free in Zero-Knowledge.** The result is Dora, a protocol for RAM zero-knowledge that transcends the seemingly inherent tradeoff between processor expressiveness (i.e.,  $|I| = \ell$ ) and execution trace length (i.e., t) altogether, and instead shows that processor expressiveness can come (nearly)  $free^{12}$ —both in terms of computation and communication.

As with prior attempts, Dora can be decomposed into a memory component and a processor instruction handling component, each of which we realize with ZKBag. Before describing the techniques that we use in Dora, we briefly recall our efficiency goals for each component:

- Efficiency Goals for Memory Component: During each step of execution, the prover will fetch (1) the value stored at the address indicated by the program counter, and (2) fetch a single value from memory and write a single value to memory, as either (or both) might be necessary for the next instruction. We require that the computation and communication complexity of each fetch and write must be constant.

- Efficiency Goals for Processor Instruction Component: During each step of execution, the prover will evaluate a single instruction on the processor state, where the instruction is determined by the value fetched in (1) above. We require that the communication and computation complexity of each step of execution is independent of |I|.

We now discuss how to achieve both of our goals using ZKBag.

**Handling Memory in** Dora **using ZKBag.** As noted above, handling memory access with ZKBag is straightforward, as ZKBag's properties are virtually identical to those required for memory consistency. The prover and the verifier

<sup>&</sup>lt;sup>11</sup>We note that there is a recent line of work showing the set membership—and disjunctive zero-knowledge more generally—can be achieved with very low overhead as the statement size grows. While it may be possible to construct ZKBag from these primitives, we instead pursue another approach discussed below.

<sup>&</sup>lt;sup>12</sup>In particular, we do not need to pay the cost of processor expressiveness at each step of the processor execution.

begin by initializing the memory space by inserting public tuples (ADDRESS, VALUE) into ZKBag for every ADDRESS in the memory space, including the program code and the rest of the initial memory state (e.g. the initial stack and heap) of the execution. When proving a step of the computation, the prover interacts with the memory store three times<sup>13</sup>:

- (1) The prover begins by reading the next instruction from memory and loading it into the processor state. This is a read-only operation, which the prover achieves by removing and re-inserting the same value (i.e. the same commitment).

- (2) The prover also reads a value from memory into the processor state in case the instruction that will be run in the next instruction needs to read memory (e.g. for a LOAD instruction). Just as above, this read is read-only. Note that the prover must always perform this read in every step of the computation in order to hide any witness-dependent read patterns.

- (3) Finally, the prover performs an update to one address in memory in case the instruction run in that step is a STORE instruction. This write instruction requires removing an element from the ZKBag and then rewriting to the same address with a new value from the processor state. <sup>14</sup> If the instruction does not require performing a write instruction, the prover can simply rewrite the initial value leaving memory functionally unchanged.

Soundness follows directly from the *unique removal* and *ordered binding* properties of the ZKBag (discussed above), as these properties guarantee that the verifier knows that each values read from memory must be "current." Zeroknowledge relies on the *order hiding* property to hide the memory addresses being manipulated.

Using this protocol, the total complexity of managing memory in Dora is only three tuple insertions and three tuple removals per step of the computation, but this can be reduced because the prover does not need to resend the same commitments multiple times.

**Handling Processor Instructions in** Dora **using ZKBag.** During each step of processor execution, the prover needs to convince the verifier that a processor state  $\mathsf{st}_{i+1}$  is the result of applying *one* of the instructions in the instruction set to the previous processor state  $\mathsf{st}_i$ , without revealing which instruction was applied. We begin by giving a baseline approach for achieving our goal before proceeding to optimize the approach to improve concrete performance.

Baseline Approach. A straightforward approach would be to use a set membership proof; the prover could generate a commitment to the executed instruction and then provide a proof that the contents of the commitment are a valid instruction. This commitment can then be added to the statement for another zero-knowledge proof that demonstrates the transition from  $\mathsf{st}_i$  to  $\mathsf{st}_{i+1}$ . This approach, while intuitive, has two primary downfalls:

- (1) While there has been a tremendous amount of work on set membership proofs, state-of-the-art protocols have a *logarithmic* size in the number of elements in the set and a *linear* computation complexity in the size of the set (e.g., [HK20c, HK20b, GGHAK22a, GGHAK22b]). While in practice it might be acceptable to tolerate the communication overhead, linear computation complexity may be unreasonable for large instruction sets. Moreover, our aim in this work is to achieve *constant* overhead—both in terms of communication and computation. While SNARKs might be a way to achieve our goals for the verifier, given SNARK's succinctness and constant-time verification, there is not an obvious way to use this set membership approach to get constant overhead for the prover.

- (2) Given a commitment to the step's instruction I, the prover must then prove that  $\operatorname{st}_{i+1}$  is the result of applying I to  $\operatorname{st}_i$ . Doing this efficiently is non-trivial, given that the statement of interest is in committed form. A very natural approach to would be to combine non-black box use of the commitment scheme and universal circuits (ie. prove that I is in the commitment and that  $U(I,\operatorname{st}_i)=\operatorname{st}_{i+1}$ , where U is a universal circuit of the appropriate size), and then prove the resulting statement using generic, circuit zero-knowledge. Unfortunately, both non-black box use of cryptography and universal circuits tend to be highly inefficient, making this approach unattractive. It might be possible to design very specific zero-knowledge proofs that naturally interoperate the chosen commitment scheme

<sup>&</sup>lt;sup>13</sup>We assume that the processor here has a simple load store architecture and all instructions in the instruction set read and write at most a single value. In more complex architectures (eg. architectures that support indirect loads) additional interactions with memory may be necessary. Supporting these instructions is trivial.

<sup>&</sup>lt;sup>14</sup>Ensuring that the read and write are to the same memory location can be easily ensured by reusing the address commitment retrieved during the removal.

to avoid the non-black box use of cryptography, but this approach would reduce the flexibility and modularity of our construction.

As such, the seemingly natural approach to handling processor instruction in Dora appears to be unfruitful. Instead, we investigate how ZKBag could be used to design a more efficient approach. As already demonstrated with memory management, ZKBag provides a highly efficient (ie. constant overhead) way to obliviously select elements from a set. As such, it seems natural to substitute the set-membership proof in the above template with ZKBag, resolving problem (1). However, using ZKBag in this way does nothing to resolve problem (2). As such, we require a slightly more nuanced approach to using ZKBag in order to achieve our result.

Combining ZKBag and Relaxed R1CS to Achieve Constant Overhead. Rather than store instructions in a ZKBag, we build on an approach from prior works on IVCs [KST22, KS22] and store a set of accumulators in the ZKBag—one accumulator for each instruction in the instruction set. Executing a step of the processor involves obliviously retrieving the appropriate accumulator from the ZKBag and updating it. The intuition behind this approach is to use these accumulators to iteratively update NP statements at each step, such that the prover can simultaneously verify the final accumulated set of  $|\mathcal{I}|$  statements at the end of the protocol. These accumulators are carefully designed such that the prover's knowledge of a valid witness at the end of the protocol for each accumulated statement demonstrates that each step was correctly executed. The benefit of this approach is that the computationally expensive zero-knowledge proofs are deferred until the end of the protocol, requiring only a single zero-knowledge proof for each instruction rather than for each step, further improving Dora's concrete efficiency.

To instantiate these accumulators, we leverage *Relaxed R1CS folding*, an approach described by [KST22]. Relaxed R1CS is a natural extension to standard R1CS such that there can be additional error terms. A typical R1CS relation is constructed by matrices  $\mathbf{A}$ ,  $\mathbf{B}$ ,  $\mathbf{C}$  and an instance  $\overrightarrow{\times}$  is satisfied if there exists a witness  $\overrightarrow{w}$  such that  $\mathbf{A} \cdot \overrightarrow{z} \circ \mathbf{B} \cdot \overrightarrow{z} = \mathbf{C} \cdot \overrightarrow{z}$ , where  $\overrightarrow{z} = \overrightarrow{w} || \overrightarrow{\times}$ . A relaxed R1CS relation injects two additional *error* parameters,  $\mathbf{u} \in \mathbb{F}$  and  $\overrightarrow{e} \in \mathbb{F}^m$ , and is satisfied if there exists a  $\overrightarrow{z} = \overrightarrow{w} || \overrightarrow{\times} || \mathbf{u}$  such that  $(\mathbf{A} \cdot \overrightarrow{z}) \circ (\mathbf{B} \cdot \overrightarrow{z}) = \mathbf{u} \cdot (\mathbf{C} \cdot \overrightarrow{z}) + \overrightarrow{e}$ . The power of relaxed R1CS is that it permits *folding*: given a fixed relation  $\mathbf{A}$ ,  $\mathbf{B}$ ,  $\mathbf{C}$ , and two instances  $(\overrightarrow{\times}_1, \mathbf{u}_1, \overrightarrow{e}_1)$  and  $(\overrightarrow{\times}_2, \mathbf{u}_2, \overrightarrow{e}_2)$ , it is possible to combine the two into a new instance  $(\overrightarrow{\times}, \mathbf{u}, \overrightarrow{e})$  for the same relation  $\mathbf{A}$ ,  $\mathbf{B}$ ,  $\mathbf{C}$ . Importantly, a prover can only satisfy the new instance  $(\overrightarrow{\times}, \mathbf{u}, \overrightarrow{e})$  if they had valid witnesses  $\overrightarrow{w}_1$ ,  $\overrightarrow{w}_2$  to the initial instances (except with negligible probability). We defer the details of this folding procedure to Section 3.2.

Dora leverages this technique as follows: the prover and verifier initialize a ZKBag and (publicly) insert a relaxed R1CS instance (as defined by  $\overrightarrow{e}$  and  $\overrightarrow{Z}$ ) for each instruction into the ZKBag that will be used as an accumulator. During each step of the computation, the prover retrieves the instance corresponding to the current instruction and prepares a new instance for the current instruction using the committed processor state and the values retrieved from memory. The prover then folds the state of the accumulator with the newly prepared instance, locally updating the witness required to satisfy the folded instance. Finally, the prover inserts the folded instance into the ZKBag and continues to the next step. After all the steps have been run, the prover removes the final accumulator for each instruction from the ZKBag and opens them to the verifier. The prover and verifier then engage in a generic zero-knowledge proof for the final relaxed R1CS instances. We note that there are several low-level details we have omitted in this description for clarity (e.g., the final instances must be randomized to satisfy zero-knowledge).

**Putting It All Together.** Dora is realized by combining the techniques described above for memory management and proving the correctness of instruction executions. In each step, the prover retrieves the appropriate values from memory and adds them to the (committed) processor state. The prover then uses the processor state to construct a relaxed R1CS instance that would prove correct execution of the instruction and folds it into the accumulator for the instruction executed in that step. Finally, the prover updates a memory location to emulate a store instruction. Once all of the steps have been completed, the prover opens all the accumulators and proves that it has a witness to each one.

We benchmark Dora in Section 8 and show that it is highly efficient. Because of its nice asymptotics, Dora can prove correct execution of RAM programs on massive processors (thousands of instruction with thousands of gates each) in milliseconds per step.

### 3 Preliminaries

In this section, we recall some prelimary definitions. In Section 3.1, we present a definition of linearly homomorphic commitments. In Section 3.3, we recall the definition of a commit-and-prove zero-knowledge protocol. In Section 3.2, we provide a formal overview of relaxed R1CS [KST22]. In Section 3.4, we recall a construction of commit-and-prove ZK for R1CS (implicit in [KST22]). Finally, in Section 3.5 we recall the construction of Neff-style [Nef01] multi-set equality proofs.

**Notation.** Let t be the number of steps in the program trace,  $\ell$  be the number of instructions in the processor circuit, m be the number of addresses in memory.

#### 3.1 Linearly Homomorphic Commitments

Our construction makes use of a standard linearly homomorphic commitment primitive, which we define below. We intentionally give a general enough definition of this primitive that can capture both *interactive* instantiations (eg. VOLE-based [BMRS21]) and *non-interactive* instantiations (eg. Pedersen [Ped92]).

**Definition 1** (Linearly Homomorphic Commitments). Linearly homomorphic commitments comprise of a tuple of four interactive protocols  $\pi^{LCom} = (\pi^{LCom}_{Setup}, \pi^{LCom}_{Commit}, \pi^{LCom}_{Open}, \pi^{LCom}_{Comb})$  between a Sender Sen and receiver Rec and a PPT algorithm Equiv defined as follows:

- $((pp, skey), (pp, rkey)) \leftarrow \pi_{Setup}^{LCom}$ : The setup protocol generates any needed public parameters pp, a sender key skey as output for the sender and a receiver key rkey as output for the receiver.

- $-((com, op), (com)) \leftarrow \pi_{Commit}^{LCom}$ : The commit protocol takes the value val to be committed as input from the sender and outputs a commitment com to both the sender and the receiver. It additionally outputs op to the sender.

- $-((b),(val')) \leftarrow \pi_{Open}^{LCom}$ : Both the sender and receiver invoke the opening protocol using a commitment com as input. The sender additionally inputs a value val committed inside this commitment and the associated opening information op. This protocol outputs a value val'  $\in \{val, \bot\}$  to the receiver and a bit  $b \in \{0,1\}$  to the sender indicating whether or not val' = val.

- $((com, op), (com)) \leftarrow \pi_{Comb}^{LCom}$ : The linear combination protocol takes  $(pp, skey, f_{lin}, com_1, op_1, com_2, op_2)$  as input from the sender and  $(pp, rkey, f_{lin}, com_1, com_2)$  as input from the receiver. It computes the function  $f_{lin}$  on  $com_1$  and  $com_2$  and outputs the resulting new commitment com and its corresponding opening information op.

- op ← Equiv<sup>LCom</sup>(pp, rkey, com, val): The equivocation algorithm and outputs the new opening information op corresponding to com and val.

We require that the scheme satisfies standard hiding. For binding, we assume that the commitment scheme has an extractor that can extract the val within a commitment. In addition to these standard properties, we assume that the  $\pi_{\text{Comb}}^{\text{LCom}}$  algorithm allows the sender and receiver to perform linear operations over commitments and we assume that the receiver can always equivocate. Formally, these properties are defined as follows:

1. **Hiding:** Let  $((pp, skey), (pp, rkey)) \leftarrow \pi_{Setup}^{LCom} \langle Sen(1^{\lambda}), Rec(1^{\lambda}) \rangle$  be an honest execution of the setup protocol. For any  $val_1, val_2 \in \mathcal{V}$ , the view of Rec remains computationally indistinguishable in the following two executions:

$$\begin{split} &\pi^{\mathsf{LCom}}_{\mathsf{Commit}} \langle \mathsf{Sen}(\mathsf{pp}, \mathsf{skey}, \mathsf{val}_1), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}) \rangle \\ &\pi^{\mathsf{LCom}}_{\mathsf{Commit}} \langle \mathsf{Sen}(\mathsf{pp}, \mathsf{skey}, \mathsf{val}_2), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}) \rangle \end{split}$$

2. **Equivocation:** Let  $((pp, skey), (pp, rkey)) \leftarrow \pi_{Setup}^{LCom} \langle Sen(1^{\lambda}), Rec(1^{\lambda}) \rangle$  be an honest execution of the setup protocol. The following holds  $\forall$  val  $\in \mathcal{V}$  and every honest execution of the commit protocol  $((com, op), (com)) \leftarrow \pi_{Commit}^{LCom} \langle Sen(pp, skey, val), Rec(pp, rkey) \rangle$ : if  $(val', op') \leftarrow Equiv^{LCom} (pp, rkey, com)$ , then for an honest sender and receiver.

$$\Pr[((1), (\mathsf{val'})) \leftarrow \pi^{\mathsf{LCom}}_{\mathsf{Open}} \langle \mathsf{Sen}(\mathsf{pp}, \mathsf{skey}, \mathsf{com}, \mathsf{op'}, \mathsf{val'}), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}, \mathsf{com}) \rangle] \geq 1 - \mathsf{neg}(\lambda)$$

3. Linear Homorphism: Let  $((pp, skey), (pp, rkey)) \leftarrow \pi_{Setup}^{LCom} \langle Sen(1^{\lambda}), Rec(1^{\lambda}) \rangle$  be an honest execution of the setup protocol. The following holds for all  $val_1, val_2 \in \mathcal{V}$ , every linear function  $f_{lin}: \mathcal{V} \times \mathcal{V} \to \mathcal{V}$  and all honest executions of the commit protocol  $(\forall i \in [2]) ((com_i, op_i), (com_i)) \leftarrow \pi_{Commit}^{LCom} \langle Sen(pp, skey, val_i), Rec(pp, rkey) \rangle$ : if

$$((\mathsf{com}, \mathsf{op}), (\mathsf{com})) \ \leftarrow \ \pi^{\mathsf{LCom}}_{\mathsf{Comb}} \left\langle \mathsf{Sen}(\mathsf{pp}, \mathsf{skey}, f_{\mathsf{lin}}, \mathsf{com}_1, \mathsf{op}_1, \mathsf{com}_2, \mathsf{op}_2), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}, f_{\mathsf{lin}}, \mathsf{com}_1, , \mathsf{com}_2) \right\rangle,$$

then for an honest sender and receiver,

$$\Pr[((1), (f_{\mathsf{lin}}(\mathsf{val}_1, \mathsf{val}_2))) \leftarrow \pi_{\mathsf{Open}}^{\mathsf{LCom}} \langle \mathsf{Sen}(\mathsf{pp}, \mathsf{skey}, \mathsf{com}, \mathsf{op}, f_{\mathsf{lin}}(\mathsf{val}_1, \mathsf{val}_2), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}, \mathsf{com}) \rangle] \ge 1 - \mathsf{neg}(\lambda)$$

4. **Binding/Extraction:** Let  $((pp, skey), (pp, rkey)) \leftarrow \pi_{Setup}^{LCom} \langle Sen(1^{\lambda}), Rec(1^{\lambda}) \rangle$  be an honest execution of the setup protocol. There exists an extractor  $\mathcal{E}$ , such that for any PPT adversary  $\mathcal{A}$  and for any com such that  $((\cdot), (com)) \leftarrow \pi_{Commit}^{LCom} \langle \mathcal{A}(pp, skey, \cdot), Rec(pp, rkey) \rangle$ , then  $(val) \leftarrow \mathcal{E}^{\mathcal{O}(\mathcal{A})}(pp)$  such that for any honest receiver and  $val \neq val' \neq \bot$ , it holds that

$$\Pr[((\cdot), (\mathsf{val'})) \leftarrow \pi^{\mathsf{LCom}}_{\mathsf{Open}} \langle \mathcal{A}(\mathsf{pp}, \mathsf{skey}, \mathsf{com}, \cdot), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}, \mathsf{com}) \rangle] \leq \mathsf{neg}(\lambda)$$

**Short-Hand Notation.** For simplicity, we use the notation  $\llbracket v \rrbracket$  denotes a commitment to some value  $\overrightarrow{v}$ . We often abuse notation and use  $\llbracket \overrightarrow{x} \rrbracket$  to denote a linearly homomorphic commitment to a vector of elements in  $\overrightarrow{x} \in \mathbb{F}^*$ . We use linear arithmetic operations as a short-hand for  $\pi^{\mathsf{LCom}}_{\mathsf{Comb}}$ , e.g.,  $\llbracket \mathsf{val} \rrbracket = c_1 \cdot \llbracket \mathsf{val}_1 \rrbracket + \llbracket \mathsf{val}_2 \rrbracket$ , where  $c_1$  is some public value. Finally, we remark that the by default, the above definition of  $\pi^{\mathsf{LCom}}_{\mathsf{Commit}}$  is presented for *private commitments*, i.e., it only takes the value to be committed as input from the sender. However, it can easily be adapted to allow for *public commitments*, where both the sender and receiver have access to the value being committed. It that case, we assume that in addition to taking val as input from both parties,  $\pi^{\mathsf{LCom}}_{\mathsf{Commit}}$  is run on shared randomness between the sender and receiver.

#### 3.2 Relaxed R1CS

Exisiting proof systems works with different representations of the relation they are proving. The most popular representation amongst state-of-the-art proof systems is known as the rank 1 constrained system (or R1CS) that generalizes arithmetic circuits. In this work, we use *Relaxed R1CS*, a generalization of R1CS introduced by Kothapalli, Setty and Tzialla [KST22]:

**Definition 2** (Relaxed R1CS, [KST22]). A relaxed R1CS (Rank-1 Constraint System) [KST22] is defined by three matrixes  $\mathbf{A}, \mathbf{B}, \mathbf{C} \in \mathbb{F}^{m \times m}$ . A witness  $\mathbf{w}$  satisfies an instance  $(\overrightarrow{\mathbf{e}}, \overrightarrow{\mathbf{x}}, \mathbf{u})$  iff. the "extended witness"  $\overrightarrow{\mathbf{z}} = \overrightarrow{\mathbf{w}} \| \overrightarrow{\mathbf{x}} \| \mathbf{u} \in \mathbb{F}^m$  satisfies:  $(\mathbf{A} \cdot \overrightarrow{\mathbf{z}}) \circ (\mathbf{B} \cdot \overrightarrow{\mathbf{z}}) = \mathbf{u} \cdot (\mathbf{C} \cdot \overrightarrow{\mathbf{z}}) + \overrightarrow{\mathbf{e}}$ . For ease of notation, refer to Relaxed R1CS instances by their extended witness  $\overrightarrow{\mathbf{z}}$  and error term  $\overrightarrow{\mathbf{e}}$ , which in turn defines  $\overrightarrow{\mathbf{w}}, \overrightarrow{\mathbf{x}}$ , and  $\mathbf{u}$ .

One valuable feature of Relaxed R1CS instances, as noted by [KST22], is that they can be "folded." That is, given two Relaxed R1CS instances  $(\overrightarrow{z_1}, \overrightarrow{e_1})$  and  $(\overrightarrow{z_2}, \overrightarrow{e_2})$  and a randomly sampled  $r \in \mathbb{F}$ , we can define a new instance  $(\overrightarrow{z}, \overrightarrow{e})$  as:

$$\overrightarrow{\mathbf{e}} = \overrightarrow{\mathbf{e}_1} + r \cdot \overrightarrow{T} + r^2 \cdot \overrightarrow{\mathbf{e}_2}, \quad \mathbf{u} = \mathbf{u}_1 + r \cdot \mathbf{u}_2, \quad \overrightarrow{\mathbf{z}} = \overrightarrow{\mathbf{z}_1} + r \cdot \overrightarrow{\mathbf{z}_2}, \text{ where}$$

$$\overrightarrow{T} = \mathbf{A} \cdot \overrightarrow{\mathbf{z}_1} \circ \mathbf{B} \cdot \overrightarrow{\mathbf{z}_2} + \mathbf{A} \cdot \overrightarrow{\mathbf{z}_2} \circ \mathbf{B} \cdot \overrightarrow{\mathbf{z}_1} - \mathbf{u}_1 \cdot \mathbf{C} \cdot \overrightarrow{\mathbf{z}_2} - \mathbf{u}_2 \cdot \mathbf{C} \cdot \overrightarrow{\mathbf{z}_1}$$

Importantly, this folding process is *sound*, in that if either  $(\overrightarrow{z_1}, \overrightarrow{e_1})$  or  $(\overrightarrow{z_2}, \overrightarrow{e_2})$  are not satisfied, then  $(\overrightarrow{z}, \overrightarrow{e})$  is also unsatisfied with high probability (over the choice of r). An additional fact about the folding scheme above (not directly used in Nova [KST22]) is that the folding *only depends on the dimensions of* A, B *and* C. This means that we can have the verifier "fold" two committed instances pairs without revealing the relation these instances belong. This will be crucial as we will be executing the folder "obliviously," in that only the prover will know which instance is being considered.

Remark (R1CS is a Special Case of Relaxed R1CS). Note that regular R1CS is captured as the special case of Definition 2 where  $\overrightarrow{e} = \overrightarrow{0} \in \mathbb{F}^m$  and u = 1. Throughout the section, to simplify notation, we will refer to relaxed R1CS instances by their error term  $\overrightarrow{e} \in \mathbb{F}^m$  and extended witness  $\overrightarrow{z} \in \mathbb{F}^m$ ; which define  $\overrightarrow{w}, \overrightarrow{x}, u$ .

### 3.3 Commit-and-Prove Zero-Knowledge

Both our final construction Dora and our subprotocol for handling processor instructions are custom-designed commitand-prove style zero-knowledge for specific languages. In this section, we recall the definition of this primitive. We assume that the commitments in this definition were computed using inearly homomorphic commitments defined in Section 3.1.

**Definition 3** (LinCom-Based Commit-and-Prove ZK). LinCom-based commit-and-prove zero-knowledge proof system for an NP-relation  $\mathcal{R}$ , comprises of a tuple of 3 interactive protocols ( $\pi_{\mathsf{Setup}}, \pi_{\mathsf{Proof}}, \pi_{\mathsf{Verify}}$ ) between the sender and receiver defined as follows:

- $((pp, skey), (pp, rkey)) \leftarrow \pi^{ZK}_{Setup}$ : The setup protocol generates any needed public parameters pp, a sender key skey as output for the sender/prover and a receiver key rkey as output for the receiver/verifier.

- $((\mathsf{Proof}^{\mathsf{ZK}},\mathsf{st}),(\mathsf{Proof}^{\mathsf{ZK}})) \leftarrow \pi^{\mathsf{ZK}}_{\mathsf{Prove}}$ : The prove protocol takes as input  $(\mathsf{pp},\mathsf{skey},\overrightarrow{x},\mathsf{com},\overrightarrow{\mathsf{op}},\overrightarrow{w})$  from the sender/prover and  $(\mathsf{pp},\mathsf{rkey},\overrightarrow{x},[\overrightarrow{w}])$  from the receiver/verifier. It outputs a proof  $\mathsf{Proof}^{\mathsf{ZK}}$  that allows the prover/sender to convince the receiver/verifier that it knows  $\overrightarrow{w},\overrightarrow{\mathsf{op}}$  such that they are a valid opening for  $[\![\overrightarrow{w}]\!]$  and  $\overrightarrow{w}$  is a valid witness for statement  $\overrightarrow{x}$ . This protocol may additionally output some secret state  $\mathsf{st}$  for the sender/prover.

- $((b),(b)) \leftarrow \pi_{\text{Verify}}^{\text{ZK}}$ : The verify protocol takes as input  $(pp, skey, Proof^{\text{ZK}}, st, \overrightarrow{x'})$  from the sender/prover and  $(pp, rkey, Proof^{\text{ZK}}, \overrightarrow{x'})$  from the receiver/verifier and outputs a bit  $b \in \{0,1\}$ , based on whether or not the proof  $Proof^{\text{ZK}}$  verifies.

We require the above protocols to satisfy the standard notions of correctness, zero-knowledge and knowledge soundness.

#### 3.4 Commit-and-Prove ZK for R1CS

Next, we recall a simple  $\Sigma$ -protocol for R1CS-satisfiability. This protocol is derived directly from the Nova [KST22] IVC scheme. This protocol satisfies all the properties that we need from a commit and prove zero-knowledge protocol defined in Section 3.3. Let  $(\mathbf{A}, \mathbf{B}, \mathbf{C})$  be an R1CS instance. Given a commitment  $[\![ \overrightarrow{\mathbf{Z}} ]\!]$ , computed using a linearly homomorphic commitment (see Section 3.1), the prover wants to convince the verifier that the value  $\overrightarrow{\mathbf{Z}} = \overrightarrow{\mathbf{W}} \| \overrightarrow{\mathbf{X}} \| \mathbf{U}$  committed inside this commitment is a valid extended witness for  $(\mathbf{A}, \mathbf{B}, \mathbf{C})$ . The setup algorithm  $\pi^{\mathsf{ZK}}_{\mathsf{Setup}}$  of this proof system is the same as the setup of the above linearly homomorphic commitment scheme. We now describe the  $\pi^{\mathsf{ZK}}_{\mathsf{Prove}}$  and  $\pi^{\mathsf{ZK}}_{\mathsf{Verify}}$  protocols.

- Prover samples a random satisified relaxed R1CS instance as follows:

- Sample  $\overrightarrow{\mathsf{z}_0} \leftarrow \mathbb{F}^m$  and parse  $\overrightarrow{\mathsf{z}_0} = \overrightarrow{\mathsf{w}_0} \|\overrightarrow{\mathsf{x}_0}\| \mathsf{u}_0$ .

- Set

$$\overrightarrow{L} \leftarrow (\mathbf{A} \cdot \overrightarrow{\mathbf{z}_0}) \circ (\mathbf{B} \cdot \overrightarrow{\mathbf{z}_0}), \overrightarrow{R} \leftarrow \mathsf{u}_0 \cdot (\mathbf{C} \cdot \overrightarrow{\mathbf{z}_0}) \text{ and } \overrightarrow{\mathsf{e}_0} \leftarrow \overrightarrow{L} - \overrightarrow{R}$$

• Prover then computes the cross terms:

$$\overrightarrow{t_1} \leftarrow \mathbf{A} \cdot \overrightarrow{\mathbf{z}} \circ \mathbf{B}_i \cdot \overrightarrow{\mathbf{z}_0} + \mathbf{A} \cdot \overrightarrow{\mathbf{z}_0} \circ \mathbf{B}_i \cdot \overrightarrow{\mathbf{z}}$$

$$\overrightarrow{t_2} \leftarrow \mathbf{u} \cdot \mathbf{C} \cdot \overrightarrow{\mathbf{z}_0} + \mathbf{u}_0 \cdot \mathbf{C} \cdot \overrightarrow{\mathbf{z}}$$

$$\overrightarrow{T} \leftarrow \overrightarrow{t_1} - \overrightarrow{t_2}$$

- Prover and verifier use  $\pi^{\mathsf{LCom}}_{\mathsf{Commit}}$  to compute commitment-opening pairs  $((\llbracket T \rrbracket, \mathsf{op}_T), (\llbracket T \rrbracket)), (\llbracket \mathsf{z}_0 \rrbracket, \mathsf{op}_{\mathsf{z}_0})$  and  $(\llbracket \mathsf{z}_0 \rrbracket, \mathsf{op}_{\mathsf{e}_0})$ .

- The verifier then samples and sends  $r \leftarrow \$ \mathbb{F}$ .

- Prover uses  $\pi_{\mathsf{Comb}}^{\mathsf{LCom}}$ ,  $\pi_{\mathsf{Open}}^{\mathsf{LCom}}$  to open the following linear combinations of the two instances:

- Let  $\overrightarrow{\mathsf{e}'}$  be the opened value associated with the commitment  $\left(r \cdot \left[\!\!\left[\overrightarrow{T'}\right]\!\!\right] + r^2 \cdot \left[\!\!\left[\overrightarrow{\mathsf{e}'_0}\right]\!\!\right]\right)$

- Let  $\overrightarrow{z}'$  be the opened value associated with the commitment  $(\overrightarrow{z} + r \cdot \overrightarrow{z_0})$

- Finally, if the above openings are valid, the verifier checks:  $\left(\mathbf{A} \cdot \overrightarrow{z'}\right) \circ \left(\mathbf{B} \cdot \overrightarrow{z'}\right) = ? = u' \cdot \mathbf{C} \cdot \overrightarrow{z'} + \overrightarrow{e'}$ , where  $u' = u + r \cdot u_0$ .

## 3.5 Multi-Set Equality Proofs

In our construction of ZKBag, we leverage an efficient set equality proof (also referred to as a permutation proof). In our concrete instantiation of Dora, we use the simple Bayer-Groth style proof. To the best of our knowledge, this construction was first documented in [Nef01] and has subsequently been independently discovered in many works [BG12, FKL+21]. Given 2 sets of commitments,  $S_1 = ([[\overrightarrow{a_1}]], \dots, [[\overrightarrow{a_k}]])$  and  $S_2 = ([[\overrightarrow{b_1}]], \dots, [[\overrightarrow{b_k}]])$ , the multi-set equality proof can be viewed as a commit-and-prove zero-knowledge protocol (say  $(\pi_{\mathsf{Setup}}^{\mathsf{ZKMultiSet}}, \pi_{\mathsf{Prove}}^{\mathsf{ZKMultiSet}}, \pi_{\mathsf{Verify}}^{\mathsf{ZKMultiSet}})$ ) for the following relation: there exists a permutation p, such that  $p(\overrightarrow{a_1}, \dots, \overrightarrow{a_k}) = \overrightarrow{b_1}, \dots, \overrightarrow{b_k}$ .

We now recall this well-known Bayer-Groth style [BG12] shuffle proof. We assume that all commitments were computed using linearly homomorphic commitments from Section 3.1. This is the only component in our construction that (black-box) relies on a general proof system – let  $\left(\pi_{\mathsf{Setup}}^{\mathsf{ZK}}, \pi_{\mathsf{Prove}}^{\mathsf{ZK}}, \pi_{\mathsf{Verify}}^{\mathsf{ZK}}\right)$  be the commit and prove zero-knowledge protocol for general R1CS satisfiability from Section 3.4. The setup algorithm  $\pi_{\mathsf{Setup}}^{\mathsf{ZKMultiSet}}$  of this proof system is the same as the setup of the above linearly homomorphic commitment scheme. We now describe the  $\pi_{\mathsf{Prove}}^{\mathsf{ZKMultiSet}}$  and  $\pi_{\mathsf{Verify}}^{\mathsf{ZKMultiSet}}$  protocols.

- Verifier samples random field elements  $u, v \leftarrow \$ \mathbb{F}$ , and sends them to the prover.

- For each  $i \in [k]$ , both the prover and verifier use  $\pi_{\mathsf{Comb}}^{\mathsf{LCom}}$  to compute

$$\llbracket \alpha_i \rrbracket = \langle (1, u^2, \dots, u^{k-1}), \llbracket \overrightarrow{a_i} \rrbracket \rangle$$

$$\llbracket \beta_i \rrbracket = \left\langle \left( 1, u^2, \dots, u^{k-1} \right), \left\lceil \overrightarrow{b_i} \right\rceil \right\rangle$$

• Finally, the prover uses  $\left(\pi_{\mathsf{Setup}}^{\mathsf{ZK}}, \pi_{\mathsf{Prove}}^{\mathsf{ZK}}, \pi_{\mathsf{Verify}}^{\mathsf{ZK}}\right)$  to convince the verifier that  $\prod_{i \in [k]} \left(v - \llbracket \alpha_i \rrbracket \right) = \prod_{i \in [k]} \left(v - \llbracket \beta_i \rrbracket \right)$ .

## 4 Zero-Knowledge Bag

The heart of Dora is a zero-knowledge bag (ZKBag) protocol. This cryptographic object is analogous to a physical bag into which the prover and verifier place wrapped objects. The critical properties of the protocol are equivalent to the physical properties that such a bag would possess: only objects previously put into the bag can be removed, and the bag itself hides the correspondence between the order in which objects are inserted and removed. In some sense, the zero-knowledge bag can be seen as a "slow moving" shuffle proof augmented with a sense of time.

### 4.1 Defining ZKBag

**Definition 4** (LinCom-Based Zero-Knowledge Bag). A ZKBag is parameterized by a linearly homomorphic commitment scheme, and as such we call the resulting cryptographic primitive a LinCom-Based ZKBag. A LinCom-Based ZKBag comprises of a tuple of 5 interactive protocols  $(\pi_{\mathsf{Setup}}^{\mathsf{ZKBag}}, \pi_{\mathsf{Init}}^{\mathsf{ZKBag}}, \pi_{\mathsf{Insert}}^{\mathsf{ZKBag}}, \pi_{\mathsf{Remove}}^{\mathsf{ZKBag}}, \pi_{\mathsf{VerEmpty}}^{\mathsf{ZKBag}})$  between the sender and receiver:

- $((pp, skey), (pp, rkey)) \leftarrow \pi_{Setup}^{ZKBag} \left\langle Sen \left( 1^{\lambda} \right), Rec \left( 1^{\lambda} \right) \right\rangle : \textit{The setup protocol generates any needed public parameters } \\ pp, \textit{generates a sender key skey as output for the sender and a receiver key rkey as output for the receiver.}$

- $((bag, state), (bag)) \leftarrow \pi_{lnit}^{ZKBag} \langle Sen(pp, skey), Rec(pp, rkey) \rangle$ : The parties take the output of  $\pi_{Setup}^{ZKBag}$  as input and initialize the ZKBag. The sender and receiver each maintain some joint information bag and the sender maintains some secret information state.

- $-\left(\left(\mathsf{bag}',\mathsf{state}'\right),\left(\mathsf{bag}'\right)\right) \leftarrow \pi_{\mathsf{Insert}}^{\mathsf{ZKBag}}\left\langle\mathsf{Sen}\left(\mathsf{pp},\mathsf{skey},\mathsf{bag},\mathsf{state},\left[\!\left|\overrightarrow{\mathsf{val}}\right|\!\right],\mathsf{op},\mathsf{val}\right),\mathsf{Rec}\left(\mathsf{pp},\mathsf{rkey},\mathsf{bag},\left[\!\left|\overrightarrow{\mathsf{val}}\right|\!\right]\right)\right\rangle: \textit{The parties take in the current state of the bag}\left(\left(\mathsf{bag},\mathsf{state}\right),\left(\mathsf{bag}\right)\right) \textit{ and a commitment }\left[\!\left|\overrightarrow{\mathsf{val}}\right|\!\right]. \textit{ Additionally, the sender provides a valid opening to the commitment }\left(\overrightarrow{\mathsf{val}},\mathsf{op}\right). \textit{ This updates the state of the bag held by both the sender and the receiver.}$

- $-\left(\left(\mathsf{bag}',\mathsf{state}'\right),\left(\mathsf{bag}'\right)\right) \leftarrow \pi_{\mathsf{Remove}}^{\mathsf{ZKBag}}\left\langle\mathsf{Sen}\left(\mathsf{pp},\mathsf{skey},\mathsf{bag},\mathsf{state},\left[\!\left[\overrightarrow{\mathsf{val}}\right]\!\right],\mathsf{op},\mathsf{val}\right), \mathsf{Rec}\left(\mathsf{pp},\mathsf{rkey},\mathsf{bag},\left[\!\left[\overrightarrow{\mathsf{val}}\right]\!\right]\right)\right\rangle: \textit{The parties take in the current state of the bag}\left(\left(\mathsf{bag},\mathsf{state}\right),\left(\mathsf{bag}\right)\right) \textit{ and a commitment }\left[\!\left[\overrightarrow{\mathsf{val}}\right]\!\right]. \textit{ Additionally, the sender provides a valid opening to the commitment }\left(\overrightarrow{\mathsf{val}},\mathsf{op}\right). \textit{ This updates the state of the bag held by both the sender and the receiver.}$

- $-\ ((b)\ ,(b)) \leftarrow \pi_{\mathsf{VerEmpty}}^{\mathsf{ZKBag}} \left\langle \mathsf{Sen}\left(\mathsf{pp},\mathsf{skey},\mathsf{bag},\mathsf{state}\right), \mathsf{Rec}\left(\mathsf{pp},\mathsf{rkey},\mathsf{bag}\right) \right\rangle : \textit{The parties take in the current state of the bag}\ ((\mathsf{bag},\mathsf{state}),(\mathsf{bag}))\ \textit{and check if the bag is empty. This outputs a bit b to the sender and the receiver.}$

We define 3 properties of these algorithms: correctness, knowledge soundness, and zero-knowledge.

1. Correctness: Correctness considers an interaction between the sender and receiver in which they run setup and initialize. After this first phase, the sender and receiver run an arbitrary sequence of inserts and removes. If there is a one-to-one correspondence between inserts and removes such that the remove always comes after the corresponding insert and the values in each corresponding pair are for the same values, then a call to \(\pi^{ZKBag}\_{VerEmpty}\) will return 1 w.h.p.

Formally speaking, let  $((pp, skey), (pp, rkey)) \leftarrow \pi_{Setup}^{ZKBag} \langle (Sen(1^{\lambda}), Rec(1^{\lambda})) \rangle$ ,  $((bag, state), (bag)) \leftarrow \pi_{Init}^{ZKBag} \langle Sen(pp, skey), Rec(pp, rkey) \rangle$  be honest executions of the setup and initialization protocols. For any  $n \in poly(\lambda)$ ,  $val_1, \ldots, val_n \in \mathcal{V}$  and any sequence of 2n executions of the insert and remove protocols such that for each  $i \in [n]$ , a protocol of the form  $\pi_{Remove}^{ZKBag} \langle Sen(\cdots, com_i, op_ival_i), Rec(\cdots, com_i) \rangle$  only appears after  $\pi_{Insert}^{ZKBag} \langle Sen(\cdots, com_i', op_i'val_i), Rec(\cdots, com_i') \rangle$  in the sequence and each of these appear exactly once, it holds that:

$$\Pr\left[((1),(1)) \leftarrow \pi_{\mathsf{VerEmpty}}^{\mathsf{ZKBag}} \langle \mathsf{Sen}(\mathsf{pp},\mathsf{skey},\mathsf{bag},\mathsf{state}), \mathsf{Rec}(\mathsf{pp},\mathsf{rkey},\mathsf{bag}) \rangle \right] \\ \geq 1 - \mathsf{neg}(\lambda)$$

Here for each  $i \in [n]$ , com<sub>i</sub> and com'<sub>i</sub> are commitments of the form:

$$\begin{split} &((\mathsf{com}_i, \mathsf{op}_i), (\mathsf{com}_i)) \leftarrow \pi^{\mathsf{LCom}}_{\mathsf{Commit}} \langle \mathsf{Sen}(\mathsf{pp}, \mathsf{skey}, \mathsf{val}_i), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}) \rangle \; \mathit{and} \\ &((\mathsf{com}_i', \mathsf{op}_i'), (\mathsf{com}_i')) \leftarrow \pi^{\mathsf{LCom}}_{\mathsf{Commit}} \langle \mathsf{Sen}(\mathsf{pp}, \mathsf{skey}, \mathsf{val}_i'), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}) \rangle. \end{split}$$

2. **Knowledge Soundness:** Knowledge soundness intuitively says that a malicious sender cannot (w.h.p.) convince the receiver that the bag is empty after an interaction unless all the restrictions on the interaction from correctness hold and the bag truly is empty. We formalize this by saying that there exists an extractor that can extract the values used in the insertions and removals, such that (as above) there is a one-to-one correspondence between inserts and removes such that the remove always comes after the corresponding insert and the values in each corresponding pair are for the same values.

Formally speaking, let  $((pp, skey), (pp, rkey)) \leftarrow \pi_{Setup}^{ZKBag} \langle (Sen(1^{\lambda}), Rec(1^{\lambda}) \rangle$  be an honest execution of the setup protocol. There exists an extractor  $\mathcal E$  such that, for any PPT adversary  $\mathcal A$ , any  $n \in poly(\lambda)$ , any execution of the initialization protocol of the form  $((\cdots), (bag_0)) \leftarrow \pi_{Init}^{ZKBag} \langle \mathcal A(pp, skey), Rec(pp, rkey) \rangle$ , and any sequence of 2n protocol executions  $(((\cdots), (bag_i)) \leftarrow \pi_{Update_i} \langle \mathcal A(pp, skey, com_i \cdots), Rec(pp, rkey, bag_{i-1}, com_i) \rangle)_{i \in [2n]}$  where each  $com_i$  is the result of invoking

$$\left( (\mathsf{com}_i, \mathsf{op}_i), (\mathsf{com}_i) \right) \leftarrow \pi^{\mathsf{LCom}}_{\mathsf{Commit}} \left\langle \mathcal{A}(\mathsf{pp}, \mathsf{skey}), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}) \right\rangle,$$

and where for each  $i \in [2n]$ , Update<sub>i</sub>  $\in \{Insert, Remove\}$ , if it holds that,

$$((1),(1)) \leftarrow \pi_{\mathsf{VerEmpty}}^{\mathsf{ZKBag}} \langle \mathcal{A}(\mathsf{pp},\mathsf{skey},\mathsf{bag}_{2n}), \mathsf{Rec}(\mathsf{pp},\mathsf{rkey},\mathsf{bag}_{2n}) \rangle$$

then  $(val_1, ..., val_{2n}) \leftarrow \mathcal{E}^{\mathcal{O}(\mathcal{A})}(pp)$ , such that if  $Index_{Insert}$  and  $Index_{Remove}$  denote the values of i corresponding to insertions and removals, then

$$\Pr\left[\exists \ a \ \textit{bijection} \ f: \mathsf{Index}_{\mathsf{Insert}} \to \mathsf{Index}_{\mathsf{Remove}}, \textit{s.t.}, \forall i \in \mathsf{Index}_{\mathsf{Insert}}, (f(i) > i) \land \left(\mathsf{val}_i = \mathsf{val}_{f(i)}\right)\right] \geq 1 - \mathsf{neg}(\lambda)$$

and for all  $i \in [2n]$ , any honest receiver Rec, and computationally bounded adversary A, and any  $\mathsf{val}_i \neq \mathsf{val}_i' \neq \bot$ , it holds that

$$\Pr[((\cdot), (\mathsf{val}_i')) \leftarrow \pi^{\mathsf{LCom}}_{\mathsf{Open}} \langle \mathcal{A}(\mathsf{pp}, \mathsf{skey}, \mathsf{com}, \cdot), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}, \mathsf{com}) \rangle] \leq \mathsf{neg}(\lambda)$$

3. **Zero-Knowledge:** Zero-knowledge says that the receiver learns nothing about the values inserted and removed, beyond the fact that the limitations from correctness are satisfied. We formalize this by saying that the view of the receiver in an honest interaction with the sender is computationally indistinguishable from an interaction with a simulator that does not know the values inserted or removed from the bag.

Formally speaking, the exists a simulator  $Sim = (Sim_{Setup}, Sim_{Init}, Sim_{Insert}, Sim_{Remove}, Sim_{VerEmpty})$ , such that for any  $n \in poly(\lambda)$ , the the view of Rec in the following sequence of protocol executions

$$\begin{split} &((\mathsf{pp},\mathsf{skey}),(\mathsf{pp},\mathsf{rkey})) \leftarrow \pi^{\mathsf{ZKBag}}_{\mathsf{Setup}} \left\langle \mathsf{Sen}(1^{\lambda}),\mathsf{Rec}(1^{\lambda}) \right\rangle \\ &((\mathsf{bag}_0,\mathsf{state}_0),(\mathsf{bag}_0)) \leftarrow \pi^{\mathsf{ZKBag}}_{\mathsf{Init}} \left\langle \mathsf{Sen}(\mathsf{pp},\mathsf{skey}),\mathsf{Rec}(\mathsf{pp},\mathsf{rkey}) \right\rangle \end{split}$$

For each  $i \in [2n]$  and arbitrary  $val_i$ :

$$((\mathsf{com}_i, \mathsf{op}_i), (\mathsf{com}_i)) \leftarrow \pi_{\mathsf{Commit}}^{\mathsf{LCom}} \langle \mathsf{Sen}(\mathsf{pp}, \mathsf{skey}, \mathsf{val}_i), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}) \rangle$$

$$\left( (\mathsf{bag}_i, \mathsf{state}_i), (\mathsf{bag}_i) \right) \leftarrow \pi^{\mathsf{ZKBag}}_{\mathsf{Update}_i} \left\langle \mathsf{Sen}(\mathsf{pp}, \mathsf{skey}, \mathsf{bag}_{i-1}, \mathsf{state}_{i-1}, \mathsf{com}_i, \mathsf{op}_i, \mathsf{val}_i), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}, \mathsf{bag}_{i-1}, \mathsf{com}_i) \right\rangle,$$

where  $Update_i \in \{Insert, Remove\}$ . And finally,

$$((1),(1)) \leftarrow \pi_{\mathsf{VerEmpty}}^{\mathsf{ZKBag}} \left\langle \mathsf{Sen}(\mathsf{pp},\mathsf{skey},\mathsf{bag}_{2n},\mathsf{state}_{2n}), \mathsf{Rec}(\mathsf{pp},\mathsf{rkey},\mathsf{bag}_{2n}) \right\rangle$$

is computationally indistinguishable from its view in the following sequence of protocol executions. For readability, we omit the state passing between the interactions, but assume that each part of the simulator and the receiver can pass arbitrary state:

$$\langle (\mathsf{Sim}_{\mathsf{Setup}}(1^{\lambda}) \leftrightarrow \mathsf{Rec}(1^{\lambda}) \rangle$$

$$\langle (\mathsf{Sim}_{\mathsf{Init}}(1^{\lambda}) \leftrightarrow \mathsf{Rec}(1^{\lambda}) \rangle$$

For each  $i \in [2n]$ :

$$\begin{split} \left( (\mathsf{com}_i, \mathsf{op}_i), (\mathsf{com}_i) \right) &\leftarrow \pi^{\mathsf{LCom}}_{\mathsf{Commit}} \left\langle \mathsf{Sim}(\mathsf{pp}, \mathsf{skey}, 0), \mathsf{Rec}(\mathsf{pp}, \mathsf{rkey}) \right\rangle, \\ & \left\langle (\mathsf{Sim}_{\mathsf{Update}_i}(1^{\lambda}, \mathsf{com}_i, \mathsf{op}_i) \leftrightarrow \mathsf{Rec}(1^{\lambda}, \mathsf{com}_i) \right\rangle \end{split}$$

$Update_i \in \{Insert, Remove\}$ . And finally,

$$\langle (\mathsf{Sim}_{\mathsf{VerEmpty}}(1^{\lambda}) \leftrightarrow \mathsf{Rec}(1^{\lambda}) \rangle$$

## 4.2 Realizing a ZKBag Protocol

We give a concrete implementation of ZKBag in Figure 1. At a high level the protocol is as follows: during setup, the parties run the setup algorithm of the underlying linearly homomorphic commitment scheme (if there is one)  $\pi^{\mathsf{LCom}}$  (see Section 3.1). During initialization, the parties just initialize three empty sets: (1) a set of committed values that were inserted into the bag  $\mathcal{I}$ , (2) a set of committed values that were removed from the bag  $\mathcal{R}$ , and (3) some private state  $\mathbb{B}$  for the sender that will hold plaintext information about the committed values. Each time a (committed) item  $\llbracket \overrightarrow{v} \rrbracket$  is inserted into the bag, the receiver samples a random tag  $\leftarrow \mathbb{F}$  and both parties add ( $\llbracket \text{tag} \rrbracket$ ,  $\llbracket \overrightarrow{v} \rrbracket$ ) to the set of "input elements"  $\mathcal{I}$ . Additionally, the sender records the tag and values by adding (tag,  $\overline{v}$ ) to  $\mathbb{B}$ . Whenever the sender

```

\underline{\left(\left(\mathsf{pp},\mathsf{skey}\right),\left(\mathsf{pp},\mathsf{rkey}\right)\right)} \leftarrow \pi_{\mathsf{Setup}}^{\mathsf{ZKBag}} \left\langle \mathsf{Sen}\left(1^{\lambda}\right),\mathsf{Rec}\left(1^{\lambda}\right)\right\rangle

• Sen and Rec invoke ((pp^{LCom}, skey^{LCom}), (pp^{LCom}, rkey^{LCom})) \leftarrow \pi_{Setup}^{LCom} \langle Sen(1^{\lambda}), Rec(1^{\lambda}) \rangle

• Output (pp = pp^{LCom}, skey = skey^{LCom}) to Sen and (pp = pp^{LCom}, rkey = rkey^{LCom}) to Rec.

((bag, state), (bag)) \leftarrow \pi_{lnit}^{ZKBag} \langle Sen(pp, skey), Rec(pp, rkey) \rangle