Cited By

View all- Hauck SDeHon A(2007)Reconfigurable ComputingundefinedOnline publication date: 2-Nov-2007

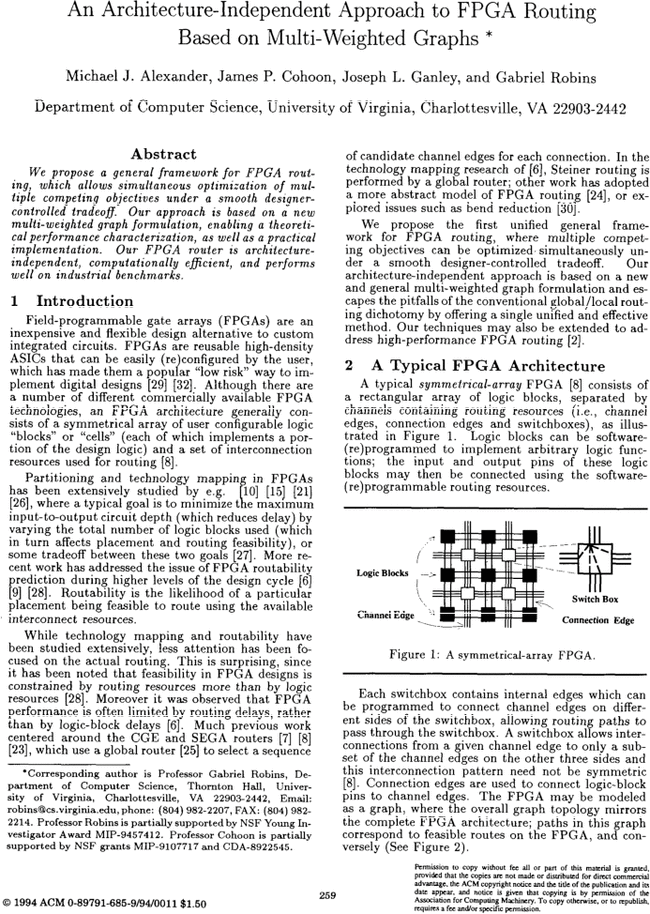

- Singh AParthasarathy GMarek-Sadowska MErnst R(2001)Interconnect resource-aware placement for hierarchical FPGAsProceedings of the 2001 IEEE/ACM international conference on Computer-aided design10.5555/603095.603122(132-136)Online publication date: 4-Nov-2001

- Parthasarathy GMarek-Sadowska MMukherjee ASingh AChristie PDavis JSylvester D(2001)Interconnect complexity-aware FPGA placement using Rent's ruleProceedings of the 2001 international workshop on System-level interconnect prediction10.1145/368640.368806(115-121)Online publication date: 1-Mar-2001

- Show More Cited By