# FORMAL VERIFICATION AND AUTOMATED MASKING OF CRYPTOGRAPHIC HARDWARE

## DISSERTATION

zur Erlangung des Grades eines Doktor-Ingenieurs der Fakultät für Informatik an der Ruhr-Universität Bochum

> by David Knichel Bochum, May 2023

Copyright © 2023 by David Knichel. All rights reserved. Printed in Germany.

To my parents, Sigrid and Jürgen, for unconditional love and endless support. And to Hannah, the love of my life.

David Knichel Place of birth: Essen, Germany Author's contact information: david.knichel@rub.de

| Thesis Advisor:    | Prof. Dr. Amir Moradi                     |

|--------------------|-------------------------------------------|

|                    | Ruhr University Bochum, Germany           |

| Secondary Referee: | Prof. Dr. François-Xavier Standaert       |

|                    | Université catholique de Louvain, Belgium |

| Tertiary Referee:  | Prof. Dr. Sebastian Faust                 |

|                    | TU Darmstadt, Germany                     |

| Thesis submitted:  | May 22, 2023                              |

| Thesis defense:    | June 19, 2023                             |

| Last revision:     | July 23, 2023                             |

# Abstract

Initially used in niche military applications, cryptography has evolved to be the indispensable foundation for guaranteeing user privacy and safety in today's data-driven and universally connected world. Technological mega trends like Artificial Intelligence (AI) and the Internet of Things (IoT) vastly accelerate the collection and processing of unimaginable amounts of personal data whose confidentiality, integrity and authenticity must be protected. Nowadays, cryptography is not only a mere extension to a system, but it even lies at the heart of many applications' functionality, for example, in the context of decentralized networks.

As a result, cryptographic algorithms are widely implemented in both soft- and hardware on a heterogeneous spectrum of devices ranging from payment cards, over key tokens and automotive platforms, to modern smartphones. As cryptographic algorithms often have to be realized within a resource-constrained context while guaranteeing high throughput and low latency, many chip vendors have started integrating cryptography as a dedicated, on-chip hardware module. Such accelerators are highly attractive as they drastically improve performance compared to sole software implementations.

While all common cryptographic algorithms are considered secure from a mere cryptanalytic viewpoint, i.e., when an adversary is limited to choosing and observing in- and outputs of the algorithm, and the execution itself is considered a black box, many works have shown that this theoretical restriction of adversarial behavior is not accurate in various realistic scenarios. In many cases, an attacker can access additional information during the execution of a cryptographic implementation, weakening the assumption of a black-box model. By passively observing the physical characteristics of a device, like the timing, the power consumption, or the electromagnetic emanation during the execution of a cryptographic algorithm, an adversary may obtain confidential information that is currently processed. We refer to attacks that leverage such unintentional relations as Side-Channel Analysis (SCA) attacks. Since their discovery, SCA attacks have proven to be highly effective for the purpose of recovering key material and breaking the security of many real-world and widespread devices.

This is why intensive focus has been laid on finding strong countermeasures. A prominent and well-studied protection against SCA is offered by the *masking* countermeasure, which, since its introduction in the context of SCA two decades ago, has received the lion's share of attention due to its sound theoretical foundation rooted in the concept of secret sharing. Here, a randomized split of the information in the processed data aims to move the successful recovery of secret keys into the practically impossible.

Achieving thorough masking in hardware is a tedious and delicate task, even for experts that can look back on many years of experience in building SCA-resistant hardware implementations. Due to the vast variety of leakage-driving physical effects within digital hardware circuits, minor errors in the design can render an implementation entirely insecure in practice. Starting from a process that mainly involved masking based on heuristics and experimental evaluation of the resulting hardware implementation through standard leakage assessment methodologies, part of the research efforts has been devoted to deriving more systematic masking approaches and evaluating designs early on in the design process. The establishment of formal adversary models, which realistically, but abstractly, model an SCA adversary's capabilities and define what information leakage can be extracted from a circuit, was a key enabler for deriving both systematic masking that can even be entirely automated, and security verification based on the netlist of the circuit. Due to its high abstraction, the robust *d*-probing model is a well studied and highly convenient SCA adversary model in the hardware context.

While generally aiming to drive advances with respect to ensuring strong protection against power-related SCA attacks, this thesis particularly presents contributions in three categories. We underline the ongoing relevance of SCA attacks – even for complex, modularized systems – by showing how combining software exploits and SCA can pose a potent threat to user privacy in widely spread consumer devices. We furthermore introduce new techniques to realize formal verification, i.e., the attestation of security and composability of masked hardware designs with respect to the formal robust *d*-probing adversary model. Last but not least, we introduce several novel schemes and methodologies for systematic and automated masking. With these, we hand an engineer a toolbox for automatically transforming any digital circuit into a circuit thoroughly protected against SCA attacks while offering high flexibility to find a suitable trade-off between security level, latency and area footprint of the resulting design.

#### Keywords.

Cryptography, Hardware Security, Side-Channel Attacks, Formal SCA Adversary Models, Masking, Composability, Formal Verification, Automation, iPhone Security

# Kurzfassung

## Formale Überprüfung und automatisierte Maskierung von Kryptografischer Hardware

Ursprünglich in militärischen Nischenanwendungen eingesetzt, hat sich die Kryptografie in der heutigen datengesteuerten und global vernetzten Welt zu einer unverzichtbaren Grundlage für die Gewährleistung der Privatsphäre und Sicherheit der Nutzer entwickelt. Technologische Megatrends wie Künstliche Intelligenz (KI) und das Internet der Dinge (IoT) beschleunigen die Erfassung und Verarbeitung unvorstellbarer Mengen personenbezogener Daten enorm. Daher ist es unerlässlich, die Vertraulichkeit, Integrität und Authentizität dieser Daten zu schützen. Kryptografie ist heute nicht mehr nur eine Erweiterung eines Systems oder einer Anwendung, sondern das Herzstück vieler Anwendungsfunktionen, z. B. im Zusammenhang mit verteilten Netzwerken.

Kryptografische Algorithmen sind sowohl in Soft- als auch in Hardware auf einem heterogenen Spektrum unterschiedlicher Geräte implementiert, welches von Zahlungskarten, über Schlüssel-Token und Automobilplattformen, bis hin zu modernen Smartphones reicht. Da kryptografische Algorithmen oft in einem ressourcenbeschränkten Kontext realisiert werden müssen und gleichzeitig ein hoher Durchsatz und eine niedrige Latenzzeit garantiert werden müssen, haben viele Chip-Hersteller damit begonnen, die Kryptografie als dediziertes On-Chip Hardwaremodul zu integrieren. Solche Hardwarebeschleuniger sind äußerst attraktiv, da sie die Effizienz im Vergleich zu reinen Softwareimplementierungen drastisch verbessern.

Während alle gängigen kryptografischen Algorithmen unter rein kryptanalytischen Gesichtspunkten als sicher gelten, d.h. wenn ein Angreifer nur die Ein- und Ausgaben des Algorithmus auswählen und beobachten kann und die Ausführung selbst als Black Box betrachtet wird, haben viele Arbeiten gezeigt, dass diese theoretische Einschränkung des gegnerischen Verhaltens in verschiedenen realistischen Szenarien nicht zutreffend ist. In vielen Fällen ist ein Angreifer in der Lage, während der Ausführung einer kryptografischen Implementierung auf zusätzliche Informationen zuzugreifen, wodurch die Annahme eines Black-Box Modells unzulässig wird. Durch die passive Beobachtung der physikalischen Eigenschaften eines Geräts, wie z. B. des Timings, des Stromverbrauchs oder der elektromagnetischen Abstrahlung während der Ausführung eines kryptografischen Algorithmus, kann ein Angreifer vertrauliche Daten beziehen, die gerade verarbeitet werden. Wir bezeichnen Angriffe, die solche unbeabsichtigten Zusammenhänge ausnutzen, als Seitenkanal(SCA)-Angriffe. Seit ihrer Entdeckung haben sich SCA-Angriffe als äußerst effektiv erwiesen, um Schlüsselmaterial zu extrahieren und die Sicherheit vieler realer und weit verbreiteter Geräte zu brechen.

Aus diesem Grund wurde ein intensiver Fokus auf die Suche nach starken Gegenmaßnahmen gelegt. Einen prominenten und gut untersuchten Schutz gegen SCA-Angriffe bietet die Gegenmaßnahme *Masking*, die seit ihrer Einführung im Zusammenhang mit SCA vor zwei Jahrzehnten aufgrund ihrer soliden theoretischen Grundlage, die auf dem Konzept des *Secret Sharings* be-

ruht, den größten Teil der Aufmerksamkeit erhalten hat. Hier zielt eine zufällige Aufteilung der Informationen in den verarbeiteten Daten darauf ab, die erfolgreiche Wiederherstellung von geheimen Schlüsseln in den Bereich des praktisch Unmöglichen zu rücken.

Das Erreichen einer soliden Maskierung in Hardware ist eine langwierige und heikle Aufgabe, selbst für Experten, die auf viele Jahre Erfahrung im Design von SCA-resistenten Hardware Implementierungen zurückblicken können. Aufgrund der großen Vielfalt von physikalischen Effekten innerhalb digitaler Hardwareschaltungen können kleine Fehler im Design eine Implementierung in der Praxis völlig unsicher machen. Ausgehend von einem Prozess, der hauptsächlich die Maskierung auf der Grundlage von Heuristiken, und die experimentelle Bewertung der Sicherheit der resultierenden Hardware Implementierung durch gängige Evaluierungsmethoden umfasste, wurde ein Teil der Forschungsanstrengungen der Ableitung systematischerer Maskierungsansätze und der Bewertung von Hardwaredesigns in einem frühen Stadium des Designprozesses gewidmet. Die Erstellung formaler Angreifermodelle, die die Fähigkeiten eines Angreifers realistisch, aber abstrakt, modellieren und abdecken, war eine wichtige Voraussetzung für die Ableitung sowohl einer systematischen Maskierung, die sogar vollständig automatisiert werden kann, als auch einer Sicherheitsüberprüfung auf der Grundlage der Netzliste der Schaltung. Aufgrund seiner hohen Abstraktion ist das robuste *d*-Probing-Modell das am meisten untersuchte und ein gut geeignetes SCA-Angreifermodell im Kontext von Hardware.

Während wir generell darauf abzielen, Fortschritte im Hinblick auf die Gewährleistung eines soliden Schutzes gegen SCA-Angriffe zu erzielen, liefert diese Arbeit insbesondere Beiträge in drei Kategorien. Wir unterstreichen die anhaltende Relevanz von SCA-Angriffen - selbst für komplexe, modularisierte Systeme - indem wir zeigen, wie die Kombination von Software-Exploits und SCA eine starke Bedrohung für die Privatsphäre der Benutzer in weit verbreiteten Endverbrauchergeräten darstellen kann. Darüber hinaus stellen wir neue Techniken vor, um eine formale Verifikation zu realisieren, d.h. den Nachweis der Sicherheit und Verschaltbarkeit maskierter Hardware Designs in Bezug auf das formale robuste *d*-Probing Angreifer-Modell. Zu guter Letzt stellen wir mehrere neue Methoden zur systematischen und automatisierten Maskierung vor. Damit geben wir Ingenieuren einen Werkzeugkasten an die Hand, mit dem sie automatisch jede beliebige digitale Schaltung in eine Schaltung umwandeln können, die gründlich gegen SCA-Angriffe geschützt ist und gleichzeitig eine hohe Flexibilität bietet, um einen geeigneten Kompromiss zwischen Sicherheitsniveau, Latenzzeit und Platzbedarf des resultierenden Designs zu finden.

#### Schlagworte.

Kryptographie, Hardwaresicherheit, Seitenkanalangriffe, formale SCA-Angreifermodelle, Maskierung, sichere Verschaltbarkeit, formale Verifikation, Automatisierung, iPhone Sicherheit

# Acknowledgements

This thesis is the result of around four years of research at the Chair for Embedded Security (EMSEC) headed by Prof. Dr.-Ing. Christof Paar, the Chair for Security Engineering (SECENG) headed by Prof. Dr.-Ing. Tim Güneysu, and the Implementation Security Group (IMPSEC) at the Ruhr-Universität Bochum under supervision of Prof. Dr. Amir Moradi.

I like to thank my family and friends. First and foremost, I want to thank my wife, Hannah. Without your emotional support, I could not have done it for sure. I met many intelligent people during this adventure, but you remain the most brilliant person I know. You mean the world to me. I love you. I also want to thank my parents, Sigrid and Jürgen. I would not be the person I am today if it was not for your unconditional support. Your love laid the groundwork for everything I have achieved. Thank you. I further like to thank my brother, Lukas, on whom I can rely without reservation and who likes to remind me that engineering is not real science. Furthermore, I want to thank my parents-in-law, Karin and Hassan, who treated me like family from the beginning and always offered refuge in their lovely home.

Next, I sincerely thank my advisor Amir Moradi for accepting me as a doctoral student and for his brilliant support. Your unwavering research interest and ability to push through boundaries are genuinely exceptional. Our many brainstorming sessions and deep discussions were the key enabler for this thesis. I appreciate that you always had an open ear, gave me a lot of freedom and trusted me concerning research and industry projects.

Moreover, I like to thank François-Xavier Standaert and Sebastian Faust for accepting to be referees for this thesis.

I am also thankful to Christof Paar and Tim Güynesu, who allowed me to be an employee of EMSEC and SECENG during my P.hD. studies. I like to thank Falk Schellenberg for invoking my interest in hardware security by supervising my bachelor thesis and later offering me a position as a student research assistant. In the same course, I thank Bastian Richter for agreeing to supervise my master thesis and for many movie and game nights outside of work.

I also thank Jennifer Knothe and Janine Hein for their lovely support. Everyone knows we would be lost without you caring for everything behind the scenes.

Now on to the IMPSEC gang: I thank Thorben Moos for always being a fun office mate and calming me down after receiving my first reviews, Felix Wegener for awaking my entrepreneurial spirit and entertaining discussions about business ideas, and Anita Aghaie for lots of joint laughter. I want to thank Aein Razei Shamirzadi for being a great office mate and companion during this adventure, and Nicolai Müller, whose 'getting-things-done' attitude is utterly impressive. A big 'thank you' also to Marvin Staib, who, despite endangering my life by introducing me to bouldering, is just a lovely person. And to Bijan Fadaeinia, who always manages to cheer me up. A special shoutout also goes to Jannik Zeitschner, my tiger; there is much more to him than meets the eye. And to Daniel Lammers, who makes me want to get my exercise and nutrition right just by being present.

I also like to thank the entire SECENG team for fun social events (In particular, Flolle for being an outstanding boat crew member), great travel memories (In particular, Georg, Jakob and Jan for a great time in California), off-topic discussions (Told you, Markus, at some point I'll get a mountainbike) and in general for the fantastic time, we all had together. I also like to thank my co-authors - in alphabetical order: Jakob Feldtkeller, Tim Güneysu, Oleksiy Lisovets, Thorben Moos, Amir Moradi, Nicolai Müller, Bastian Richter and Pascal Sasdrich. Thank you for all the great collaborations.

I wish all of you nothing but the best for your future.

# **Table of Contents**

| Imprint          | • | . v    |

|------------------|---|--------|

| Abstract         | • | . v    |

| Kurzfassung      | • | . viii |

| Acknowledgements | • | . xi   |

### I Preliminaries

1

| 1 | <b>Intro</b><br>1.1<br>1.2<br>1.3 |                  |                                                 | <b>3</b><br>3<br>7<br>7<br>7 |

|---|-----------------------------------|------------------|-------------------------------------------------|------------------------------|

|   |                                   | $1.3.2 \\ 1.3.3$ | Formal Verification of Masked Circuits          | $9\\12$                      |

|   |                                   | 1.3.3<br>1.3.4   | Methodologies and Tooling for Automated Masking | 12 $15$                      |

| 2 | Bac                               | kground          | d                                               | 17                           |

|   | 2.1                               | Notati           | ion                                             | 17                           |

|   | 2.2                               | Crypte           | ography                                         | 18                           |

|   |                                   | 2.2.1            | Asymmetric Cryptography                         | 18                           |

|   |                                   | 2.2.2            | Symmetric Cryptography                          | 18                           |

|   |                                   | 2.2.3            | Block Ciphers                                   | 20                           |

|   |                                   | 2.2.4            | Practical Block Cipher Constructions            | 20                           |

|   | 2.3                               | Side-C           | Channel Analysis Attacks                        | 21                           |

|   |                                   | 2.3.1            | Physical Attacks                                | 21                           |

|   |                                   | 2.3.2            | SCA Threat Model and Security Goal              | 21                           |

|   |                                   | 2.3.3            | Power Side Channel                              | 22                           |

|   |                                   | 2.3.4            | Experimental Leakage Assessment                 | 23                           |

|   |                                   | 2.3.5            | Correlation Power Analysis                      | 25                           |

|   | 2.4                               | SCA (            | Countermeasures                                 | 26                           |

|   |                                   | 2.4.1            | Hiding Countermeasure                           | 27                           |

|   |                                   | 2.4.2            | Masking Countermeasure                          | 27                           |

|   | 2.5                               | Forma            | ll SCA Adversary Models                         | 28                           |

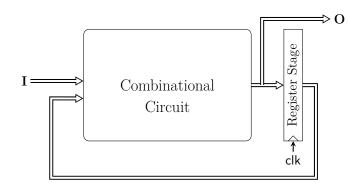

|   |                                   | 2.5.1            | Circuit Model                                   | 28                           |

|   |                                   | 2.5.2            | Noisy Leakage Model                             | 29                           |

|   |                                   | 2.5.3            | Random Probing Model                            | 30                           |

|   |                                   | 2.5.4            | d-Probing Model                                 | 30                           |

|     |                    | <ul> <li>2.5.5 Bounded Moment Model</li></ul>                                                                                                           | $\frac{32}{33}$ |

|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|     | 2.6                | Automated Hardware Masking and Composability Notions                                                                                                    | $\frac{33}{34}$ |

|     | 2.0                | 2.6.1 Handcrafted Masking and Experimental Evaluation                                                                                                   | 35              |

|     |                    | 2.6.2 Towards Sound and Systematic Hardware Masking                                                                                                     | 35              |

|     |                    | 2.6.3 Gadget-Based Masking                                                                                                                              | 37              |

|     |                    | 2.6.4 Composability Notions                                                                                                                             | 37              |

|     |                    | 2.6.5 Gadget Realizations                                                                                                                               | 41              |

|     |                    | 2.6.6 Discussions on the Costs of Automated Masking                                                                                                     | 43              |

|     | 2.7                | Formally Verifying SCA Resistance and Secure Composability                                                                                              | 43              |

|     |                    | <ul> <li>2.7.1 Pre-Silicion Verification Methodologies for Hardware</li></ul>                                                                           | 43<br>44        |

| II  | Pu                 | blications                                                                                                                                              | 47              |

| 3   | <b>Pers</b><br>3.1 | sistent Threat of Side-Channel Analysis Attacks<br>Let's Take it Offline: Boosting Brute-Force Attacks on iPhone's User Authenti-<br>cation through SCA | <b>49</b>       |

|     |                    |                                                                                                                                                         |                 |

| 4   |                    | mal Verification of Masked Hardware Circuits                                                                                                            | 75              |

|     | 4.1                | SILVER - Statistical Independence and Leakage Verification                                                                                              | 75              |

|     | 4.2                | Transitional Leakage in Theory and Practice – Unveiling Security Flaws in Masked Circuits                                                               | 107             |

| 5   | Nov                | el and Securely Composable Hardware Modules for Masking                                                                                                 | 133             |

|     | 5.1                | Generic Hardware Private Circuits – Towards Automated Generation of Com-                                                                                |                 |

|     |                    | posable Secure Gadgets                                                                                                                                  | 133             |

|     | 5.2                | Composable Gadgets with Reused Fresh Masks – First-Order Probing-Secure                                                                                 | 157             |

|     | 5.3                | Hardware Circuits with only 6 Fresh Masks                                                                                                               |                 |

|     | 0.0                |                                                                                                                                                         |                 |

| 6   |                    |                                                                                                                                                         | 203             |

|     | 6.1                | Automated Generation of Masked Hardware                                                                                                                 | 203             |

| 111 | Co                 | onclusions                                                                                                                                              | 247             |

| 7   | Con                | clusions and Open Problems                                                                                                                              | 249             |

| IV  | Ар                 | pendix                                                                                                                                                  | 251             |

| Bi  | bliog              | raphy                                                                                                                                                   | 253             |

| List of Abbreviations                | 265 |

|--------------------------------------|-----|

| List of Figures                      | 267 |

| List of Tables                       | 269 |

| About the Author                     | 271 |

| Publications and Academic Activities | 275 |

Part I Preliminaries

# Chapter 1

## Introduction

The scope and contributions of this work are outlined below. We discuss the importance of providing robust protection against side-channel attacks. In this context, we further motivate the need to formally verify hardware components regarding their side-channel resistance and secure integration into larger circuits. We also highlight the drawbacks of handcrafted, heuristic protection mechanisms in the context of masking, and emphasize the need for systematic techniques to achieve practical side-channel protection.

#### Contents of this Chapter

| 1.1 | Motivation                | 3 |

|-----|---------------------------|---|

| 1.2 | Structure of this Thesis  | 7 |

| 1.3 | Our Research Contribution | 7 |

### 1.1 Motivation

The surge in demand for microchips, driven by the Internet of Things (IoT), Artificial Intelligence (AI), and the automotive transformation to autonomous driving, underscores the trend toward ubiquitous connectivity in a data-driven world. Its current scale far outstrips supply, which is further exacerbated by the increasing complexity of systems, shaky supply chains and a persistent talent shortage [BdJD22, BKP<sup>+</sup>22].

Considering autonomous driving as a highly relevant example of large-scale communication networks based on real-time data collection and processing, secure vehicle-to-vehicle communication in compliance with fundamental security goals such as confidentiality, integrity, authenticity and availability is crucial to ensure user safety and privacy. For performance reasons, such complex systems, which involve a large number of communication nodes, use heterogeneous cryptographic primitives, typically combining asymmetric cryptography for the establishment of a secure communication channel and symmetric cryptography for the actual high-throughput communication over this channel.

While today's established ciphers are considered secure in a purely cryptanalytic sense, i.e., there are no known possible key recovery attacks in a black-box scenario where the adversary is limited to choosing arbitrary plaintexts and observing the corresponding ciphertexts without gaining any information about the computation itself, their real-world integration into larger systems has proven to be highly inconsistent with these assumptions. This leaves the implementation and integration of cryptographic algorithms vulnerable to broad physical attack vectors in many scenarios, thus compromising security and potentially having far-reaching consequences with respect to a system's security and privacy guarantees.

Even though there has been a long and deep research effort to protect cryptographic implementations against these types of physical attacks, the countermeasures themselves and the process of thoroughly protecting implementations are still far from reaching their optimum in terms of efficiency and cost-effectiveness, ensuring a continued high relevance for achieving further improvements.

Consequently, several factors are crucial to consider in this context. A practical and continuous assessment of the relevance of physical attacks and their threats is important to cover the majority of attack vectors and scenarios. Furthermore, it is essential to reduce the cost of implementing solid countermeasures, and it is highly beneficial to optimize the development process, since resources in terms of money, time and expertise are tied up in realizing thorough protection against these types of attacks. This thesis aims to make progress on all of these factors.

**Silicon Root of Trust.** The integrity of a system and the guarantee that it will boot in a secure and trusted state is rooted in the hardware components involved and the secret key material stored on them. Therefore, it is crucial that the keys remain secret and unaltered, even in the presence of physical access, such as during shipping. A system's trust is therefore anchored in the lowest level of its components: The silicon of the hardware. While the majority of chip vendors offer some form of silicon root of trust, Google and its partners have launched the *OpenTitan* project [JRR<sup>+</sup>18] with the goal of developing an open source root of trust through design and implementation transparency, underscoring the strong need for a trustworthy hardware foundation. Since the security guarantees of a complex system ultimately fall back on the security of the hardware, it is crucial to build a silicon root of trust that is thoroughly protected against all kinds of physical attack vectors.

**Cryptograhic Hardware Accelerators.** Driven by increasing functionality requirements and decreasing technology size, Integrated Circuits (ICs) and Printed Circuit Board (PCB) designs are becoming increasingly complex, making it difficult to perform thorough security evaluations. To ensure high throughput and confidential communication between devices, general-purpose computing units are often paired with dedicated symmetric encryption logic, either in a completely separate IC or on the same die in the form of a System on Chip (SoC). Examples of such accelerators are Intel's and AMD's AES-NI [HC12], but Apple's iPhones are also equipped with dedicated AES hardware realizations placed within their Application Processor (AP) and Secure Enclave Processor (SEP) [App22], which are crucial components in the root of trust and are involved in the boot, user authentication and data encryption processes.

**Cost of Hardware Development and Production.** Security integration and evaluation are important factors to consider when estimating the development and production costs of a new IC design. In general, the cost of manufacturing and developing ICs can be broadly divided into one-time costs and recurring costs per IC. Minimizing fixed, non-recurring costs is important for

low-volume and highly specialized ICs. According to this categorization, security-related nonrecurring costs include labor costs for expensive security specialists and security evaluation. At the same time, the increased area required to integrate protection mechanisms drives recurring production costs. Finding new ways to optimize both is a highly relevant goal of ongoing academic research and the semiconductor industry. It is therefore crucial not only to thoroughly protect the hardware implementation against physical attacks, but also to establish a scientific basis for implementing countermeasures in an economically viable way, thus lowering the barrier for integrating important protection mechanisms. Such a lower burden will lead to a wider application of robust protection, even for devices of smaller product lines.

**Side-Channel Analysis Attacks.** At a high level, SCA refers to attacks in which the adversary exploits unintended dependencies between sensitive data stored on or processed by a cryptographic device and the physical characteristics of the device. The term cryptographic device simply describes a device that performs some form of cryptographic operation, like an encryption, or stores cryptographic key material [MOP07]. Cryptographic devices include generealpurpose microcontroller, reconfigurable hardware (Field Programmable Gate Arrays (FPGAs)) and Application Specific Integrated Circuits (ASICs) – possibly in combination. While there are many more, common examples of exploitable features include timing [Koc96], power consumption [KJJ99] and electromagnetic radiation [GMO01]. Passively observing and analyzing these physical properties often allows an adversary to completely extract secret key material from smart cards [MOP07], smart phones [BFMT16, VMC19, LKMM21] and other critical hardware systems [EKM<sup>+</sup>08, KKMP09, OP11, ORP13, SRH16]. Although the threat model initially assumed direct physical access to the device, more and more research has been published that relaxes this requirement by introducing fully remote attack vectors [SGMT18, ZS18, SGMT21], further expanding the scope of dangerous attack scenarios and highlighting the need for adequate protection mechanisms. In this thesis, we focus on power-related SCA on symmetric algorithms realized as a digital hardware circuit.

**Masking as a SCA Countermeasure.** In general, mitigation strategies for SCA aim to weaken the dependency between confidential data and the leaking physical characteristics (the side channel) to such an extent that obtaining useful information becomes impractical for any realistic adversary. Besides *hiding* [MOP07], which relaxes this dependency more directly through technical means, e.g., by increasing electrical noise or equalizing power consumption for different secret states or operations, *masking* is a prominent and well-studied SCA countermeasure on an algorithmic level [ISW03, Tri03, NRS11, RBN+15, GMK17, GM18, SM21]. Rooted in the concept of secret sharing [Sha79], sensitive data is split into independent, random shares, and the cryptographic operation is then performed on the shares instead of the secret itself. Intuitively, this splitting of information makes recovery much more difficult (and, if properly implemented, even prohibits practical SCA altogether), but it is non-trivial to implement and introduces high overhead into the design in terms of latency and area footprint.

**Formal Adversary Models.** To formally argue about the resilience of a hardware design against SCA, various adversary models have been introduced over time, aiming to real-istically model a real-world SCA adversary while working at different levels of abstraction [ISW03, FGP<sup>+</sup>18, DDF19, BDF<sup>+</sup>16, DFS15]. The main advantage of introducing formal

adversarial models is twofold. First, given sufficient abstraction, it allows for the systematic formulation of new masking algorithms and methods in provable compliance with security in the adversary models. Second, it allows evaluating the security of a design with respect to the formal adversary model. This security assessment can be made very early in the design cycle, on the synthesized netlist of a masked implementation. Assuming that the model accurately covers a real adversarial scenario, practical SCA resilience can be guaranteed or verified prior to production, eliminating the need for multiple iterations after experimental security verification fails, and as a consequence drastically reducing cost and time to market.

**Securely Composable Gadgets and Automated Masking.** Masking large circuits that realize complex, nonlinear functions such as ciphers has proven to be extremely difficult. Even for experts with years of experience in SCA and masking countermeasures, the process of masking such designs is highly error-prone. Since minor errors can render a design completely insecure in practice [MMSS19], a major branch of research with respect to masking focuses on establishing more systematic and automatable ways to achieve SCA resilience [ISW03, BBD<sup>+</sup>16, CS20]. Here, with a solid theoretical foundation based on formal adversary models, masked hardware modules have been developed that guarantee SCA resilience even when interconnected to form a larger circuit. These building blocks – commonly referred to as hardware *gadgets* in the literature – are then used to mask any given circuit in a divide-and-conquer fashion. The underlying process can even be completely automated. Many of these building blocks realize masked versions of atomic functions like an AND gate. Still, they can be instantiated for arbitrary security levels, eventually enabling the systematic masking of arbitrary digital circuits at any desired security level.

**Formal Verification.** The traditional approach to verifying an implementation's resistance to SCA relies heavily on experimental security verification after IC fabrication. The goal of this experimental verification is to identify any dependencies between a given physical characteristic (such as electromagnetic radiation or power consumption) and a secret currently stored on or processed by the device. This is done by statistical analysis of actual experimental measurements. Since this type of practical verification requires going through all the steps of the hardware design process, including layout and fabrication, a design that turns out to be insecure in practice must be adjusted before fabrication is repeated. Obviously, this iterative process is very costly and time consuming. Accurate formal adversary models make it possible to evaluate the level of protection against SCA very early in the design process. Typically, it can be performed at the netlist level after the Register Transfer Level (RTL) description has been synthesized with respect to a specified gate library, eliminating the need for a try-and-error approach and drastically reducing the resources required in terms of time and cost. Assuming that the adversary model accurately captures all realistic SCA attack scenarios, software tools for formally verifying the security of an implementation through its netlist are highly beneficial for achieving SCA resilience in an effective and efficient manner [BGI<sup>+</sup>18, BBC<sup>+</sup>19, KSM20, MM22, BMRT22].

**Cost Reduction and Use-Case Specific Requirements.** While achieving SCA resilience through masking is an important goal in itself, making it practical, i.e., achieving it at a reasonable cost and guaranteeing sufficient throughput and speed, is ultimately the more relevant

objective. Compared to handcrafted masking based on heuristics and experience, fully automated masking typically introduces significant overhead into the design in terms of randomness requirements, additional latency and the area footprint of the protected circuit. The area footprint (and randomness requirements since some sort of randomness source with sufficient throughput must be provided on-chip) translates directly into the cost of producing cryptographic ICs. At the same time, low latency is important for specific use cases such as fast memory encryption. The creation of an improved and diverse library of hardware gadgets is highly important to enable automated masking with reduced production costs and to tailor the protected design to a specific use case.

### 1.2 Structure of this Thesis

This thesis is divided into three main parts. The first chapter in Part I contains the introduction to our work, giving a general motivation, followed by this section, and finally summarizing the main research contributions in Section 1.3. The following chapter of this part, Chapter 2, provides all the scientific concepts used throughout this thesis, including elaborations on symmetric cryptography, side-channel analysis and countermeasures, formal side-channel adversary models, automated masking and composability notions as well as formal verification of sidechannel resistance. Part II contains all the scientific publications that are part of this thesis. Each publication is preceded by a brief summary of its content, the publication details and a summary of the contributions made by the author of this thesis. This chapter is divided into four topical sections that form the basis of this thesis. Chapter 3 deals with the persistent threat of side-channel analysis, before publications dealing with the formal verification of masked hardware modules for masking in Chapter 4. This is followed by our research on new composable hardware modules for masking in Chapter 5 and our publication on novel methods and tools for automated masking in Chapter 6. Part III summarizes this work and discusses open issues that may be addressed in future work.

### 1.3 Our Research Contribution

Generally, all research contributions made by the scientific publications forming this thesis aim to effectively and efficiently protect hardware against power-related SCA attacks. This objective is founded on four pillars. First, we elaborate on new SCA attack scenarios in the context of widespread end-consumer targets. Second, we introduce new methodologies and tools for verifying a hardware design's resilience against SCA solely based on the netlist representation of the circuit. Subsequently, we present a set of novel masked hardware modules that can be freely combined without compromising security guarantees, before we present new techniques for enabling and improving the automated generation of masked circuits.

#### 1.3.1 Persistent Relevance of SCA and Novel Threat Models

A continuous evaluation of possible new threat scenarios with respect to physical attacks in modern and complex hardware architectures is crucial to ensure high security of widely used devices. Therefore, part of the focus of this thesis is to elaborate on the relevance of side-channel attacks on complex and modularized consumer devices that are based on various hardware and software components.

Advances in SCA Attack Scenarios on Widespread Consumer Devices [LKMM21]. Published work on practical power side-channel attacks on consumer devices has become rare due to the immense increase in complexity of modern ICs and SoCs, accompanied by the increased difficulty of performing successful SCAs attacks. Smartphones are good examples of such complex architectures. We show that when it comes to the security of complex systems, hardware and software cannot be considered independently, and that there are manifold attack vectors that combine both to form a powerful lever for privacy exploitation.

To ensure that a complex system boots into an intended state, the boot process is divided into several steps that together form a chain of trust. Each step guarantees the integrity of the next. This chain typically starts with a minimal piece of software embedded in the chip that cannot be updated by firmware updates. This immutable piece of software is used to validate the integrity of any software that is subsequently loaded. Together with the hard-fused key material used for validation, this piece of software forms the root of trust. Changing this chain or obtaining key material from the hardware can have immense consequences for the security of a system, as it allows the boot process to be altered and modified software to be loaded. Therefore, in complex environments, security analysis of hardware and software should never be considered separately.

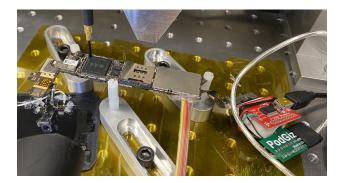

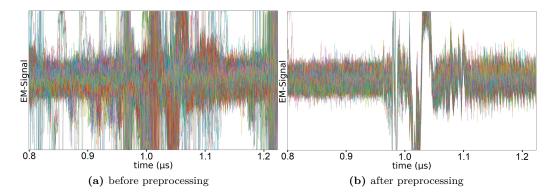

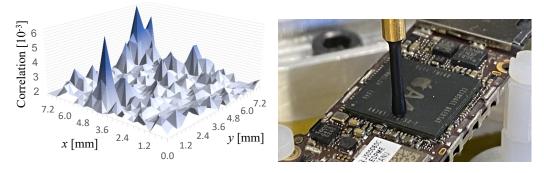

In our work, we use a public BootROM exploit on an iPhone 4 to run our own software on the device, with the goal of gaining oracle access to the iPhone's AES core. By oracle access, we mean that we can trigger an unlimited amount of encryptions and decryptions on chosen input data. This oracle access allows us to perform SCA attacks on the iPhone 4's hardware-fused key material. We perform an SCA based on the Electro-Magnetic (EM) emanation of the AP as well as an attack based on the imminent power consumption. In addition to the Group Identifier (GID), a key that is identical across devices of the same model and is involved in guaranteeing the integrity of the operating system, we successfully recover the so-called Unique Identifier (UID) key, which is device-specific and plays a crucial role in user authentication. More specifically, it cryptographically binds the user authentication to be performed on the device. This process is intentionally designed to take some time (about 80ms [App12]) to create a hardware barrier to brute forcing the user's passcode. Once the key is recovered, the passcode search can be performed offline and is arbitrarily scalable with respect to the underlying resources. Without any advanced optimizations, we show that using multiple Graphical Processing Unit (GPU)s dramatically accelerates the brute force search compared to on-device computation. For example, we reduce the worst-case runtime for a common six-digit number from 22 hours to only 26 seconds using 8 GeForce RTX2080 TIs [NVI18].

Thus, with this work, we highlight the importance of continuously evaluating consumer devices for possible implementation attacks and implementing appropriate countermeasures that protect against all types of attack scenarios in the context of complex systems involving various hardware and software components. We do this by presenting the following main contributions:

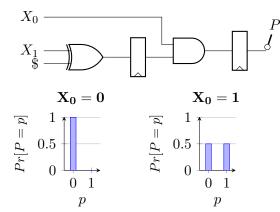

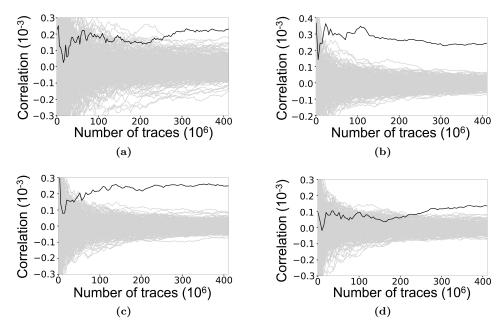

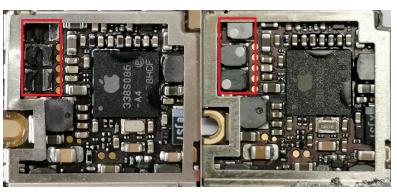

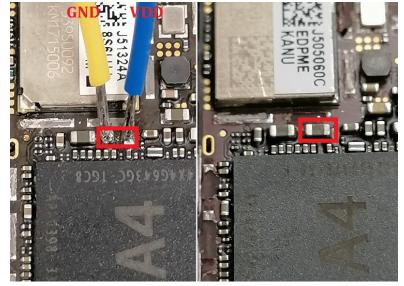

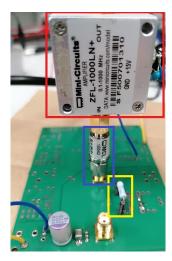

(i) Successful recovery of the GID and UID key from an iPhone 4 by performing a Correlation Power Analysis (CPA) attack. A picture showing the setup for the CPA, including the EM probe used, can be seen in Figure 1.1.  (ii) Significant gain over an on-device brute-force passcode search, boosted by several GPUs, since the extraction of the UID allows it to be performed offline. The results are given in Table 1.1.

Figure 1.1: CPA setup: EM probe placed on the AP of the iPhone 4 [LKMM21].

| $\mathbf{digits}$ | iPhone     | 1xGPU      | $8 \times GPU$ |

|-------------------|------------|------------|----------------|

| 4                 | 13 minutes | 2 seconds  | < 1 second     |

| 6                 | 22 hours   | 3 minutes  | 26 seconds     |

| 7                 | 9 days     | 35 minutes | 4 minutes      |

| 8                 | 92 days    | 5 hours    | 43 minutes     |

| 9                 | 925 days   | 58 hours   | 7 hours        |

| 10                | 25 years   | 24 days    | 3 days         |

| 11                | 253 years  | 243 days   | 30 days        |

| 12                | 2536 years | 2439 days  | 304 days       |

Table 1.1: Runtime comparison of passcode search: on-device vs. GPU cluster. GPU = RTX 2080 TI [LKMM21].

#### 1.3.2 Formal Verification of Masked Circuits

Traditionally, evaluating the resilience of cryptographic hardware implementations against SCA attacks has been, and often still is, purely experimental. However, a purely experimental approach has the disadvantage that production must be fully completed before a core can be evaluated. If the evaluation indicates an inadequate level of security, the design must be adjusted accordingly. This iterative methodology can be extremely costly and time-consuming. In addition, it is immensely difficult to identify the source of the vulnerability by analyzing the results of the experimental evaluation alone.

Using formal adversary models, we can evaluate the SCA resilience of a cryptographic hardware core very early in the design process, at the netlist level of a circuit. In contrast to an experimental setup, formal adversary models further abstract from a specific technology, platform and environment, hence allowing for a worst-case security evaluation. While experimental security guarantees are always in the context of the used evaluation setup and environment, formal adversary models enable a more general security statement.

In this thesis, we therefore introduce novel verification techniques to guarantee a thorough SCA resilience early in the design process of a new cryptographic implementation.

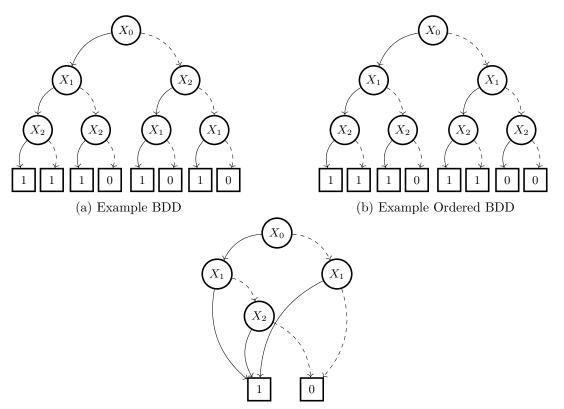

A Complete and Accurate Tool for Verifying Security and Composability in the Robust d-Probing Adversary Model [KSM20]. We have develop a novel methodology for analyzing security and composability in the formal *d*-probing model [ISW03] and its robust variant [FGP<sup>+</sup>18]. Our technique allows to perform thorough SCA resilience checks at the netlist level of an implementation, thus detecting security flaws early in the circuit design process. To achieve this, we translate all security and composability notions into a unified form based on evaluating the statistical independence between observations and (unshared) circuit inputs. We then use socalled Binary Decision Diagrams (BDDs) [Jr.78] which are well-established data structures for circuit analysis performed in the context of Electronic Design Automation (EDA). These data structures allow us to check for such statistical independence and thus evaluate security with respect to the formal security and composability notions considered. We have implemented our results in the form of a tool called SILVER. At the time of publication, SILVER was the first *complete* and *accurate* tool for security verification in the context of the formal glitch-extended robust *d*-probing model. It is *complete* in the sense that it covers all common formal notions of security and composability. It is *accurate* in the sense that it does not produce false positive or false negative results. Of course, if a design is claimed to be secure, it is crucial that it really is secure, i.e., that it conforms to the security definition of the *d*-probing model. On the other hand, other existing formal verification tools, such as maskVerif [BBC<sup>+</sup>19], allow false negatives, i.e., designs that are claimed to be insecure by the tool are actually secure in the *d*-probing model. This is because the security check is performed in an overly conservative manner to achieve a reduction in verification complexity. The downside of allowing such false negatives is that it can introduce unnecessary overhead into a circuit, because in practice an engineer will tweak the circuit until the tool indicates its security. With SILVER, we get an accurate security statement at the cost of reduced efficiency. For this reason, SILVER is most useful for evaluating smaller hardware designs in the context of composability notions.

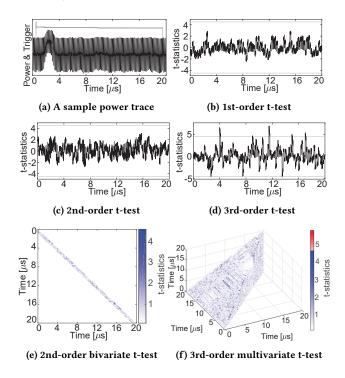

In addition to indicating the security and secure composability of a hardware circuit, SILVER provides additional information to the user. If the circuit is insecure or non-compliant with one or more composability notions, SILVER provides the cause of the problem in the form of leaking probes. This is a very useful piece of information, as it makes it much easier to locate the source of the problem. In practical leakage assessments, it is expected that the noisy sum of all wires will be observed during a single clock cycle [CJRR99]. Since many operations are performed in parallel during a single clock cycle in hardware, the exact leakage source cannot be detected by a classical Test Vector Leakage Assessment (TVLA).

With this work, we have further improved the formal verification of hardware circuits. In particular, the accuracy and the support of all common composability notions have proven to be very useful in practice and have paved the way for much follow-up work on automation and efficient designs – by us and within the research community. With our work we achieve the following main contributions:

- (i) Unifying the methodology for checking security and composability notions in the glitchextended robust d-probing model using statistical independence.

- (ii) Introducing SILVER, a software tool that, based on a circuit's netlist, can evaluate security in the glitch-extended d-probing model along with all common composability notions (Non-Interference (NI) [BBD+15],Strong Non-Interference (SNI) [BBD+16] and Probe Isolating Non-Interference (PINI) [CS20]). It is also capable of checking the output uniformity [Bil15] of a circuit.

- (iii) SILVER provides precise information about the origin of the leakage.

- (iv) As SILVER works on the synthesized netlist of a hardware design, it is perfectly suited to be integrated into established EDA design flows and tool chains.

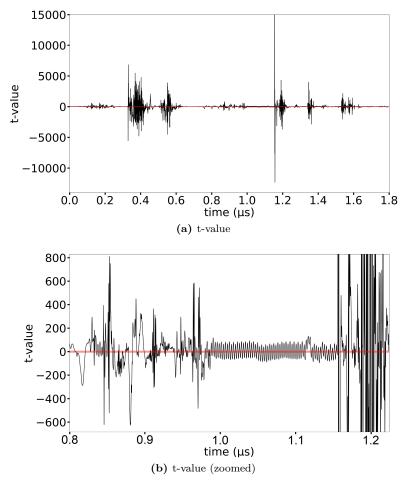

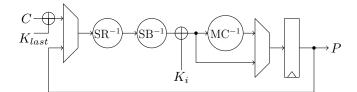

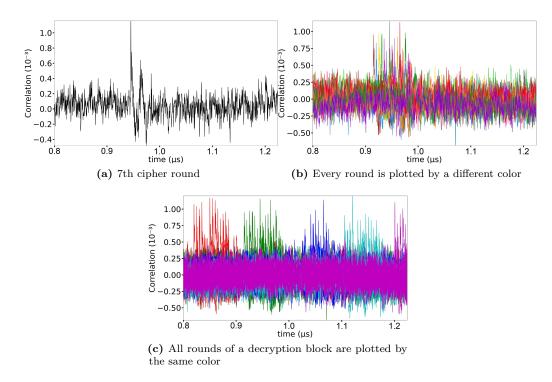

Covering Data Transitions on Registers in the Context of Formal Verification [MKSM22]. Data transitions at registers are known to be a major source of information leakage in hardware designs. Therefore, they are abstractly covered in a worst-case manner in the context of the (robust) d-probing model [FGP<sup>+</sup>18]. This abstraction allows for a simple security check under

| Scheme                          | Latency | Randomness                | Function                            | Reference |

|---------------------------------|---------|---------------------------|-------------------------------------|-----------|

| HPC1                            | 2       | $d(d+1)/2 + r[d]^\dagger$ | AND                                 | [CGLS21]  |

| HPC2                            | 2       | d(d+1)/2                  | AND                                 | [CGLS21]  |

| <b>GHPC</b> *                   | 2       | m                         | $f:\mathbb{F}_2^n\to\mathbb{F}_2^m$ | [KSM22]   |

| $\mathbf{GHPC}_{\mathbf{LL}}^*$ | 1       | $2^n \cdot m$             | $f:\mathbb{F}_2^n\to\mathbb{F}_2^m$ | [KSM22]   |

| HPC3                            | 1       | d(d+1)                    | AND                                 | [KM22b]   |

${}^{\dagger}r[d] = [1, 2, 4, 5, 7, 9, 11, 12, 15, 17] \text{ for } d \le 10$  ${}^{*}$  restricted to d = 1

Table 1.2: Comparison of existing PINI-composable and glitch-robust Hardware Private Circuits (HPCs). Gadgets in **bold** were published in the course of this thesis. d denotes the security order.

transitions by simply adding an additional preprocessing step to the probing sets placed on a sequential circuit.

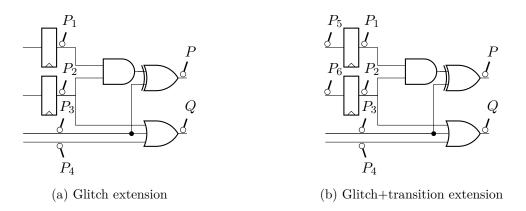

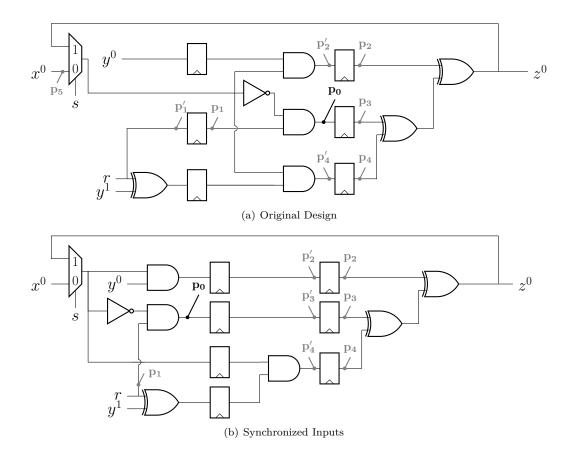

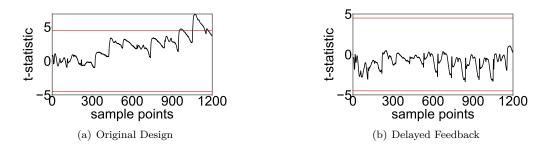

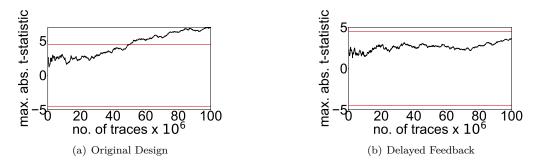

While formal hardware verification tools had already covered glitches as a common physical effect in hardware that facilitates leakage, consideration of transitions at registers and the combination of transitions and glitches remained very rudimentary. Since our initial methodology for SILVER also lacks any consideration of transitions, we extend our initial work and include support for transitions in the original version of the tool.

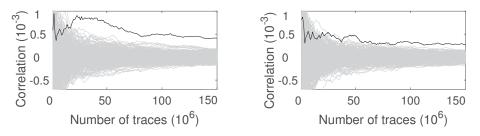

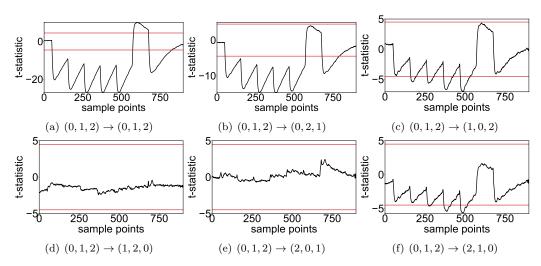

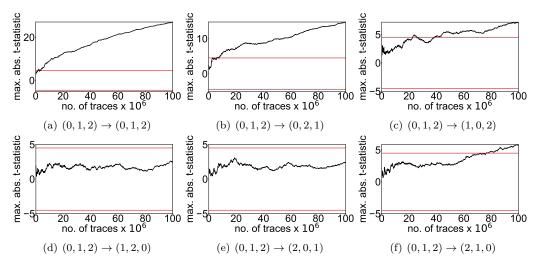

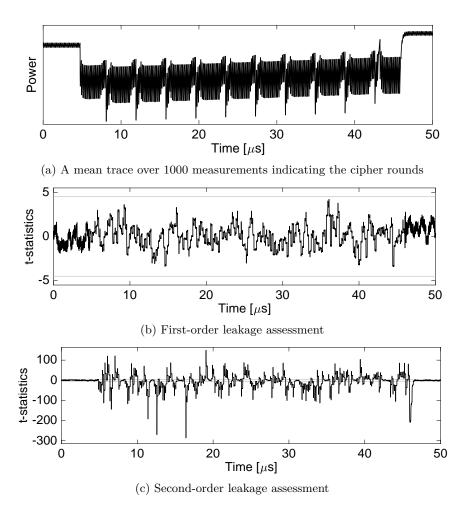

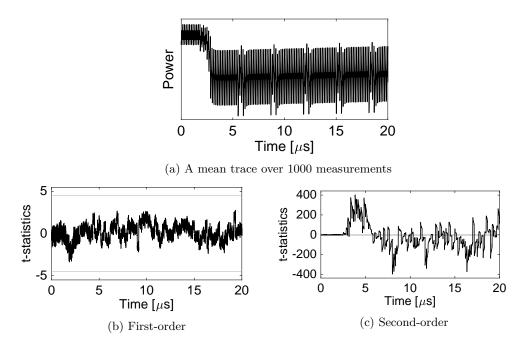

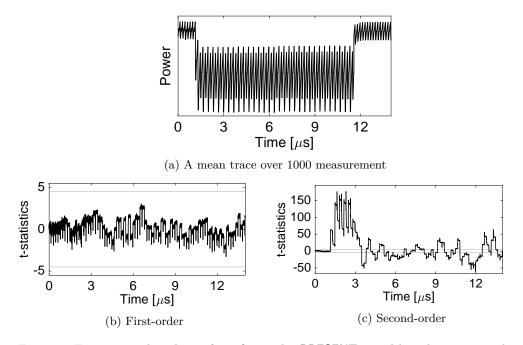

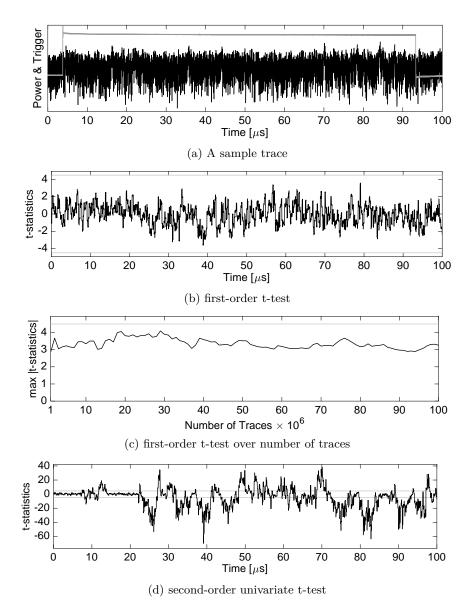

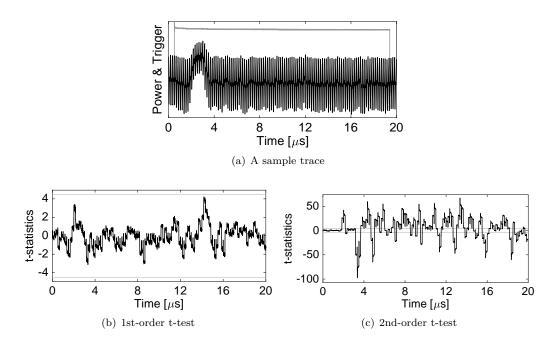

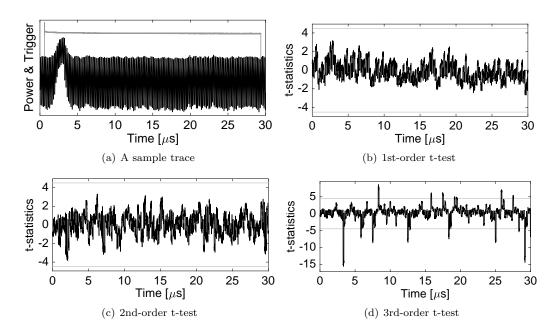

More precisely, we extend SILVER to support sequential, iterative circuits, where the same physical module can be executed multiple times with respect to the same input, and where a sequence of different inputs must be considered accurately. We also adapt our probe extension methodology to adequately cover the occurrence of transitions and the combination of glitches and transitions. This extension allows us to analyze various designs found in the literature and identify leakage caused solely by transitions at registers. We are able to confirm our tool-based findings by performing practical elaborations on top.

With this work, we highlight the importance of considering transitions when formally verifying hardware designs. We show that, while transitions lead to insecurity when not considered appropriately, adding a lot of additional overhead into the design just to handle transitions can be unnecessary in many cases. With our new version of SILVER, we are able to circumvent both cases, further paving the way for efficient and effective masking countermeasures.

Our main contributions are summed up in the following:

- (i) We derive a new technique for handling transitions and the combined occurrence of glitches and transitions for iterative circuits that can be fed by a sequence of different inputs.

- (ii) We extend SILVER to support our new methodology and study various masked circuits and schemes from the literature for their (in)sufficiency in handling transitions appropriately.

#### 1.3.3 Novel and Securely Composable Hardware Modules for Masking

Securely masking large and complex circuits is a delicate and error-prone task, especially when higher security orders are considered. Therefore, securely composable hardware modules – commonly referred to as *gadgets* – can provide a crucial building block for creating larger hardware components that are thoroughly protected against SCA attacks in a divide-and-conquer fashion. In the course of this thesis, we have developed several new gadget constructions, all of which offer different trade-offs with respect to the overhead metrics of a masked circuit. Consequently, the contributions made in this part of the thesis aim to give a researcher or engineer more flexibility to tailor a masked circuit to a specific use case. For example, reducing latency as much as possible may be a requirement when implementing memory encryption. Another requirement might be to make the masking as inexpensive and therefore as small as possible, while still achieving a very high level of security. All our designs aim to provide more freedom in the systematic design of masked circuits.

**Extending the Functionality of Trivially Composable Hardware Modules [KSM22].** Until the publication of our work, freely composable gadgets were limited to implementing very basic functionality. They typically represented masked variants of atomic logic gates, such as a simple two-input AND or OR.

Being restricted to such gadgets with limited functionality has the significant drawback that each gadget introduces individual overhead – such as randomness requirements, area footprint and latency – into a design. Since a large number of gadgets is required to realize complex circuits such as entire encryption cores, this naturally results in a significant final overhead for the protected implementations.

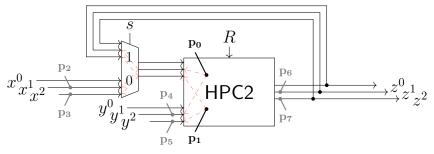

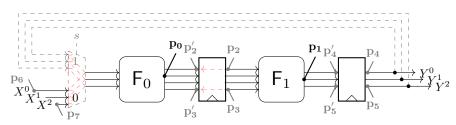

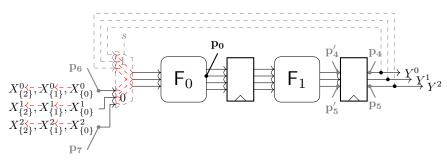

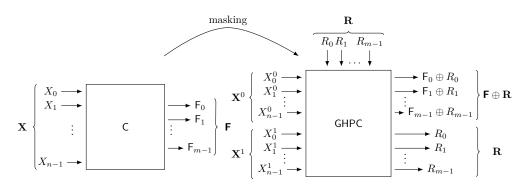

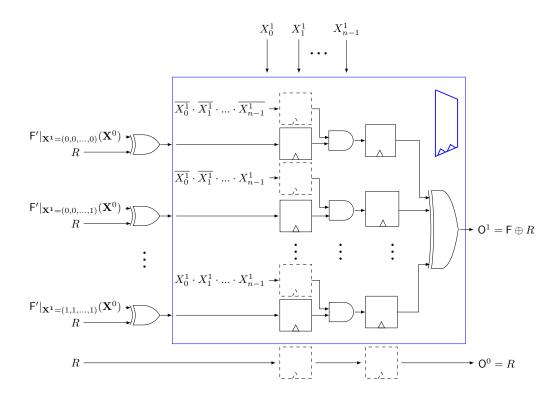

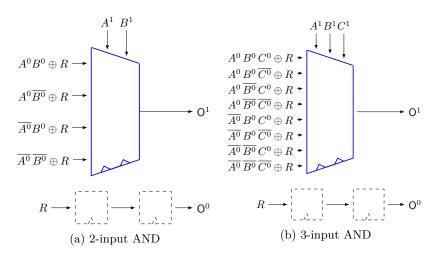

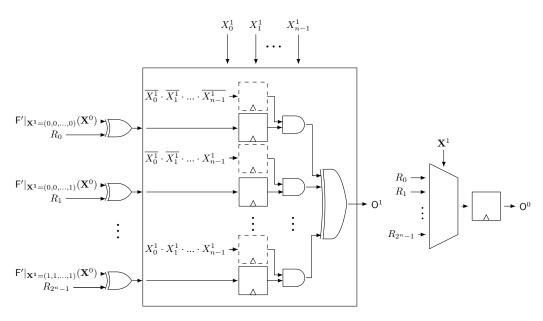

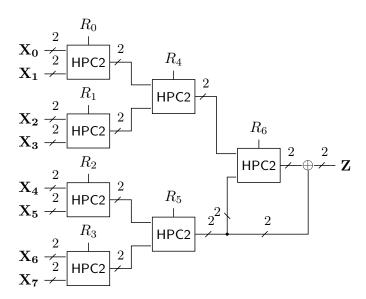

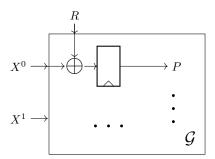

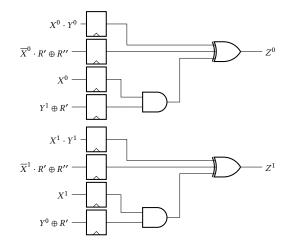

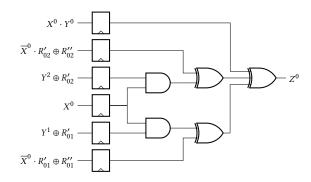

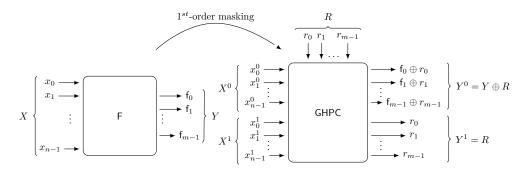

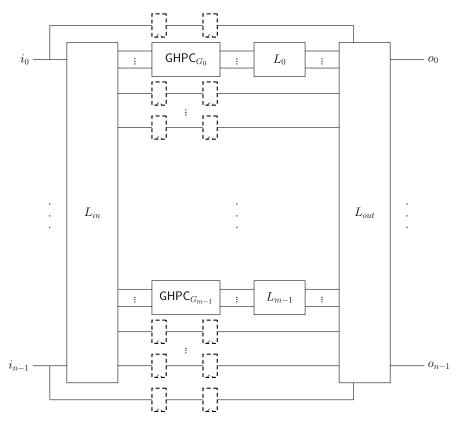

In our work, we focus on extending the functionality that composable gadgets can provide while not drastically increasing the randomness and latency overhead over existing atomic gadgets. With our novel construction called Generic Hardware Private Circuit (GHPC), we introduce a methodology to realize gadgets that are freely composable under the notion of PINI [CS20] in the glitch-extended robust probing model with arbitrary functionality. Such gadgets can be easily derived based on the functional description, i.e., the vectorial Boolean function, it should realize. While restricting our considerations to the first security order, we introduce two variants of our technique.

In its standard variant, GHPC allows to realize any functionality with only two register stages and one fresh random bit per coordinate function. Our low-latency variant – denoted  $GHPC_{LL}$ – allows to build a gadget for any functionality with *n* unshared inputs, using only a single register stage, but consuming  $2^n$  random bits per coordinate function. A comparison with other PINI-composable hardware gadgets can be seen in Table 1.2. It should be noted that the area complexity grows exponentially with the number of inputs to the circuit. For this reason, it is advantageous to avoid building very large functions as GHPCs, but to adjust the tradeoffs between latency, randomness and area requirements by adjusting the complexity of the gadgets in terms of their functional scope. For example, we can realize a complete S-box as a single GHPC with a rather large area footprint but low latency and low randomness requirements, or we can reduce the area by further dividing the S-box into functional blocks and then building GHPCs for those blocks. We also like to emphasize that our introduced constructions are freely composable with any other existing PINI-composable gadget, thus further extending their range of application.

As a result, our novel GHPC constructions hand an engineer more flexibility for masking a circuit based on composable gadgets, and allow the creation of a custom gadget library where gadgets can be selected based on the use case and what trade-off between fresh randomness, latency and area footprint is required.

Our work provides the following key advantages over the state of the art:

- (i) We introduce GHPC our standard variant: A generalized construction that allows building first-order, PINI-composable hardware gadgets for arbitrary vectorial Boolean functions. This variant requires only a single fresh random bit per coordinate function and has a latency of two clock cycles.

- (ii) We introduce GHPC<sub>LL</sub> our low-latency variant: A generalized technique for building firstorder, PINI-composable hardware gadgets for arbitrary vectorial Boolean functions. This variant requires 2<sup>n</sup> fresh random bits per coordinate function, where n is the number of unshared inputs, while requiring only a single cycle latency.

**Freely Composable Gadgets with Randomness Reusage [KM22a].** The randomness requirements of masked circuits ultimately translate into area overhead, since a dedicated randomness source must be placed on-chip. This source must be able to provide sufficient throughput for the required randomness supply. To ensure a secure design, each random bit supplied to a composed circuit must be renewed every clock cycle in the context of common and widely used gadget designs and composability notions. Because a large number of gadgets is typically required to implement full encryption – each with individual randomness requirements – gadget-based masking typically results in designs that require a high-throughput randomness source.

While a generic cost function for generating randomness has never been derived, meaning that there is no lower bound on the area required to implement a randomness source capable of providing a given throughput, it is an interesting topic to reduce the randomness requirements of masked circuits and evaluate the resulting overall area gain in terms of a common implementation of a randomness source.

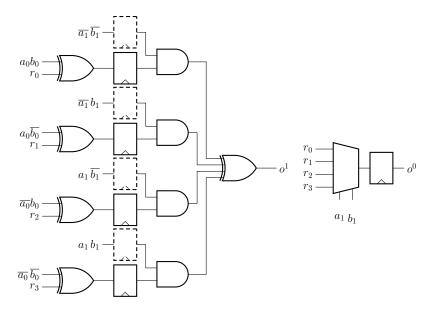

One way to reduce the overall randomness requirements of a circuit is to construct gadgets that allow the reuse of random bits across gadget boundaries.

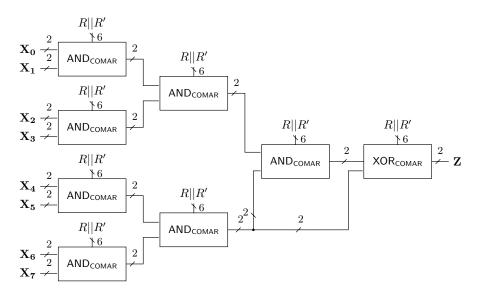

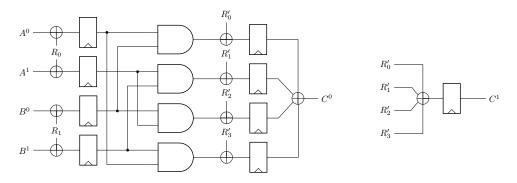

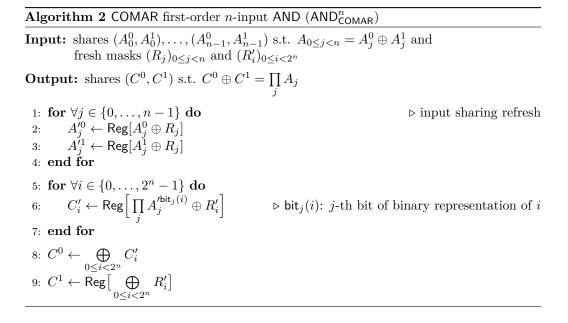

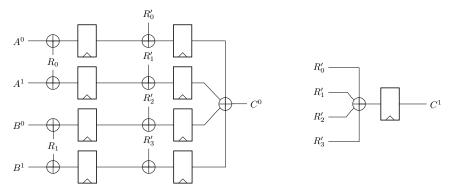

In our work, we introduce COMAR, a methodology that leads to a set of novel gadget constructions that implement all common atomic logic gates in a masked fashion, and allow us to construct any circuit that is protected for the first security order in the glitch-extended robust probing model. This allows us to reduce the number of required fresh bits to a total of six, completely independent of the complexity and size of a circuit. This means that we can build any protected circuit using a total of only six fresh random bits, not including the randomness needed to share the input to the circuit.

While paying the price of increased latency, we show that if the randomness supply is implemented as a Linear Feedback Shift Register (LFSR), which is common practice in comparable literature, we can achieve significant reductions in the area consumption of the overall design, i.e., when considering the encryption core together with the LFSRs.

In addition, we show that the input width of our COMAR gadgets can be arbitrarily increased without significantly increasing the overall randomness requirements. This is simply due to the

fact that the total requirements are only determined by the maximum requirements of a single gadget, since all random bits can be reused across gadgets. Widening the input width does not increase the latency of a gadget, but it generally allows the design to be fine-tuned for a better latency/area tradeoff.

With COMAR, we offer another tool for systematic masking that effectively decouples the randomness requirement of a first-order masked circuit from its size and complexity, allowing arbitrary circuits to be masked using a total of only six random bits. This is another step in the direction of giving a designer more flexibility to tailor a circuit to a particular use case.

Our work makes the following main contributions to freely composable gadgets with randomness reuse:

- (i) A freely first-order composable AND gadget that can be instantiated for arbitrary input widths. Gadgets for other nonlinear logic gates can be trivially derived from this AND gadget.

- (ii) A freely first-order composable XOR gadget, also instantiable for arbitrary input widths.

- (iii) Random bits are fully reusable across gadgets. If the circuit instantiates nonlinear COMAR gadgets with at most n inputs and linear COMAR gadgets with at most m inputs, the number of fresh mask bits required for the entire circuit is max(n,m) + max(2n, 2m). If we only use two-input gadgets, this results in an overall requirement of only six fresh random bits.

**Low-latency Hardware Private Circuits [KM22b].** Latency – in terms of the number of clock cycles required for an input to produce the desired output – is an important factor in synchronous circuit design. Low latency is desirable in many applications, such as fast memory encryption. Glitches in the robust *d*-probing model are one of the main drivers of latency, as registers must be carefully placed to avoid unwanted information leakage due to signal recombinations caused by such physical effects.

Since composability notions limit leakage for each gadget individually, each gadget instantiation introduces latency into the design. In the context of PINI [CS20], the overall latency is determined by the path within the circuit that contains the most nonlinear atomic gates, since linear operations can be performed in a trivial, share-wise manner and do not contribute additional latency to the design.

Intuitively, the length of such a path is determined by the algebraic degree of the Boolean function the circuit is realizing, and is quite large for cryptographic primitives, for example in the context of AES, which uses an 8-bit S-box. While [CGLS21] shows how global optimizations in the context of HPC2 gadgets can actually reduce the overall latency for small 4-bit S-boxes by taking into account the asymmetry in the input-output latency of the gadgets, no PINI-composable gadget had a single clock cycle latency for all inputs.

In our work, we introduce HPC3, a PINI-composable gadget that realizes a masked variant of an AND gate and is instantiable for arbitrary security orders. Compared to the state of the art, HPC3 has a latency of only a single clock cycle, making it highly advantageous in low-latency use cases. The decrease in latency we achieve comes at the cost of doubling the randomness requirements compared to HPC2. An overview of PINI composable gadgets is presented in Table 1.2. We also present a variant of HPC3 that is composable under the Ouput Probe-Isolating Non-Interference (O-PINI) notion introduced in [CS21] with the aim of guaranteeing trivial composition under the combined occurrence of glitches *and* transitions. As evaluated as part of this thesis [MKSM22], its practical use is mainly limited to specific edge use cases.

As a result, our work offers new constructions for the systematic creation of masked circuits, which is advantageous in use cases where latency is a critical factor. The main advances of our work are as follows:

- (i) We present HPC3: A PINI-composable hardware gadget that implements a masked variant of an AND gate and can be initialized at arbitrary security orders. It has a latency of only a single clock cycle, while doubling the randomness requirements compared to the state of the art, i.e., HPC2 gadgets.

- (ii) This allows us to achieve a significant latency reduction for gadget-based masking compared to comparable work.

#### 1.3.4 Methodologies and Tooling for Automated Masking

Securely masking large and complex circuits is a difficult task, especially when considering higher security orders. It requires extensive experience and time. Achieving solid protection through handcrafted masking based solely on heuristics is extremely difficult for higher security orders, which is underscored by the lack of published work presenting such heuristically derived designs that are secure for security orders greater than three.

Therefore, a systematic and automatable masking approach based on a divide-and-conquer methodology that allows to mask arbitrary circuits at any desired security order has been part of the focus within the research community. Such a methodology is based on composable hardware modules, of which we present several novel variants in this thesis.

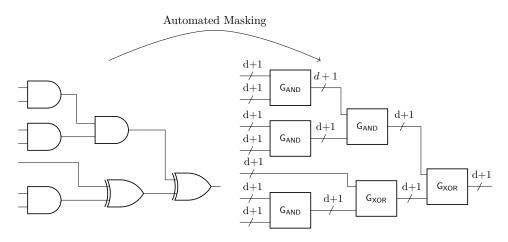

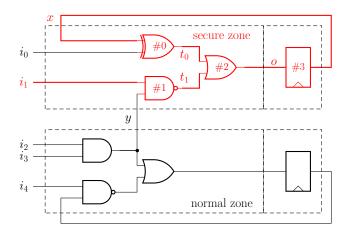

The simple underlying idea is based on the replacement of unprotected gates by their masked and securely composable counterparts: The corresponding hardware gadgets. Since these counterparts fulfill well-defined theoretical properties that guarantee security when composed together, the derived circuit will be provably SCA resistant with respect to the (robust) *d*-probing adversary model.

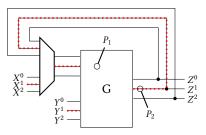

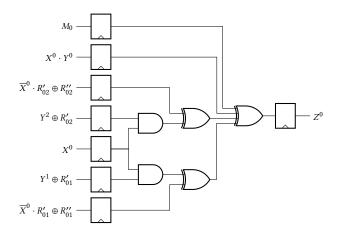

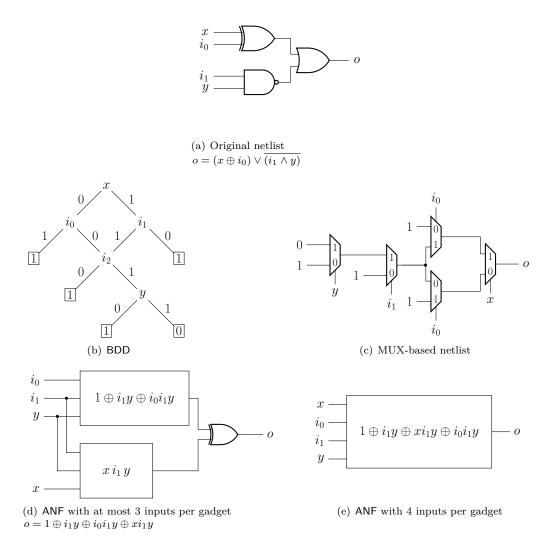

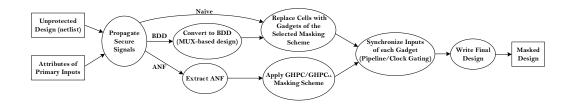

Automated Masking of Unprotected Circuits [KMMS22]. In our work, we present a tool for automated hardware masking that effectively relies on a simple divide-and-conquer approach.

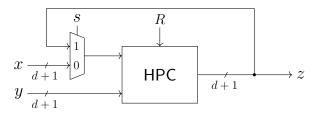

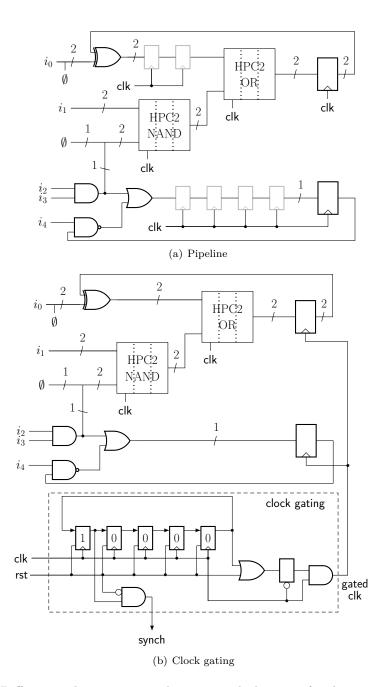

Our tool, called AGEMA, is based on composable gadgets. In fact, AGEMA works on a custom library of PINI-composable gadgets that can be easily extended by any novel constructions, as long as they fulfill the notion of PINI [CS20]. Basically, AGEMA takes the netlist of an unprotected circuit as input and outputs a circuit that is secure in the formal glitch-extended d-probing model [FGP<sup>+</sup>18]. It is possible to configure various parameters that define not only how the unprotected circuit is preprocessed before being masked, but also the security order. In general, it is possible to mask a circuit for any desired security order, while arbitrary security orders are not possible for all preprocessing methods. Since gadgets introduce individual latencies into the design, AGEMA users can choose between two different synchronization techniques. If higher throughput is desired, the design is pipelined, while clock gating can be used to achieve a more compact circuit design.

An extensible library of gadgets, together with our various preprocessing methods, enables the rapid generation of protected hardware, while providing many options for customizing the implementation to best suit the needs of a specific use case. This allows engineers to find favorable tradeoffs between randomness requirements, area footprint and latency. Integration of future, novel PINI-composable gadgets is straightforward, as they can be easily integrated into the custom gadget library.

At the time of publication, AGEMA was, to the best of our knowledge, the first fully automated tool for turning any entirely unprotected hardware design into a design thoroughly protected against SCA attacks, offering provable security guarantees in the context of the (robust) *d*-probing model. We should highlight that the process only needs a few seconds.

As a consequence, with our work, we present the following main advances:

- (i) We introduce AGEMA: A tool for fully automated masking of unprotected circuits. The result is guaranteed to be secure in the glitch-extended robust d-probing model. AGEMA is able to achieve security for arbitrary security orders.

- (ii) Introduction and thorough comparison of different preprocessing techniques for the unprotected circuit and elaboration of their influence on the resulting, masked circuit.

- (iii) AGEMA is well suited for direct integration into existing EDA tool chains.

# Chapter 2

# Background

In this chapter, we provide the scientific foundation necessary for our work. We give an introduction to physical attacks, in particular SCA attacks. In this context, we will give a detailed description of existing abstract adversary models and explain the masking countermeasure, before describing the concept of composability notions and how they can be used for systematic and automated masking. Finally, we will show how the SCA resilience of a hardware design can be formally verified in the context of the corresponding adversary model.

#### **Contents of this Chapter**

| Notation                                                   | <b>17</b>    |

|------------------------------------------------------------|--------------|

| Cryptography                                               | <b>18</b>    |

| Side-Channel Analysis Attacks                              | <b>21</b>    |

| SCA Countermeasures                                        | <b>26</b>    |

| Formal SCA Adversary Models                                | <b>28</b>    |

| Automated Hardware Masking and Composability Notions       | <b>3</b> 4   |

| Formally Verifying SCA Resistance and Secure Composability | <b>43</b>    |

|                                                            | Cryptography |

## 2.1 Notation<sup>1</sup>

Capital letters usually denote random variables. In the context of masking, we indicate share indices by subscripts, while input indices are identified by superscripts, e.g.,  $X_i^j$ , denotes the random variable describing the *i*-th share of the *j*-th input. Calligraphic font is used to denote sets, while vectors are written in bold. We usually denote the number of shares as *s*. We denote the vector of all valid Boolean sharings of a specific value  $x \in \mathbb{F}_2$  by  $Sh(x) = \{\mathbf{x} = (x_0, x_1, \ldots, x_{s-1}) | \bigoplus_{i=0}^{s-1} x_i = x\}$ . We denote all shares from a set S corresponding to input *j* by  $S^j$ . While we use  $Pr[\cdot]$  for denoting the probability, we otherwise use common notation for statistical concepts like dependencies. We use  $E(\cdot)$  for the expectation operator. Assignments to variables – that are possibly the result of a randomized processes – are indicated by ' $\leftarrow$ '. If we want to highlight a deterministic assignment, we use ':='. We further denote drawing *X* independently and uniformly from  $\mathcal{R}$  by  $X \stackrel{\$}{\leftarrow} \mathcal{R}$ .

$<sup>^{1}</sup>$ May differ from the notation used in Part II. The notation of the included publications is always declared within the publication.

### 2.2 Cryptography

While the concept of secret messages goes back a long way, and rudimentary encryption devices existed as early as ancient Greece, a more formal and broader consideration emerged in the early 20th century and was accelerated by the introduction of computers and the digitization [Dav97]. While cryptography was originally concerned with keeping messages between two parties secret in an information-theoretic sense, modern-day cryptography is a vibrant area of research that spans a variety of scientific disciplines, from mathematics to information technology, computer science and electrical engineering. A simple definition can be found in [PP09]: "Cryptography is the science of secret writing with the goal of hiding the meaning of the message." While this definition captures the important goal of *confidentiality*, modern cryptography aims to achieve a much wider range of goals, including data *authenticity* and *integrity*.

Differing in their key distribution mechanism and efficiency, *symmetric* and *asymmetric* ciphers together form the fundamental building blocks of modern cryptographic protocols that are utilized for secure communication.

#### 2.2.1 Asymmetric Cryptography

Introduced in 1976 by W. Diffie, M.Hellmann and R. Merkle, asymmetric cryptography, or public-key cryptography, drastically simplifies key management compared to symmetric approaches [DH76]. In contrast to symmetric cryptography, each identity is assigned a key pair: a public and a private key. The public key can then be stored in an accessible way, for instance on a server, and can be utilized by any other identity to encrypt or verify messages. All of the traditional asymmetric schemes rely on one of three mathematical problems: integer factorization, discrete logarithm and the elliptic-curve discrete logarithm problem. As these problems are strongly expected to be efficiently solvable with the emergence of practical and sufficiently powerful quantum computers [Sho97], current research is fully concentrated on establishing novel post-quantum schemes that guarantee thorough security in a future age of widespread quantum computers. Asymmetric cryptography is commonly applied for modern signature schemes and key exchange protocols. Because of its limited throughput, it is not directly used for data encryption in most cases. Instead, a symmetric and shared key is derived by means of a key exchange protocol which is based on asymmetric key pairs. This combines the advantages of both symmetric and asymmetric schemes by providing efficient key management while fast data encryption is guaranteed. Such hybrid approaches are widely applied in modern complex system architectures like IoT systems or inter-vehicle communication.

#### 2.2.2 Symmetric Cryptography

Symmetric ciphers are the main building blocks for guaranteeing high-throughput and confidential communication between two parties through symmetric encryption schemes. Fundamentally, a symmetric encryption scheme can be defined according to Definition 2.2.1.

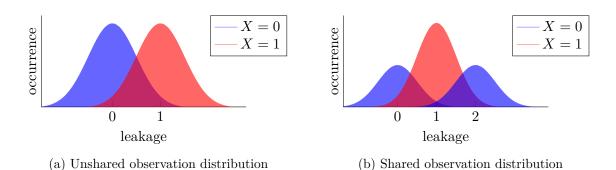

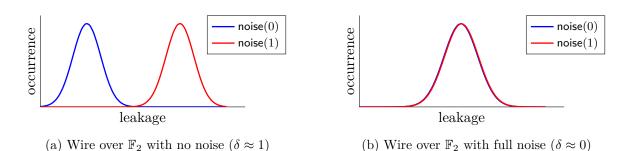

**Definition 2.2.1** (Symmetric Encryption Scheme [KL14]). A symmetric (or private-key) encryption scheme is a tuple of probabilistic polynomial-time (p.p.t.) algorithms (GEN, ENC, DEC) that are defined as follows: